LEON: a new recipe for chips

How to go about designing a microprocessor? The first step is to think about what it needs to do, in this case serve as a general purpose processor for space-based computer systems.

The next, having selected the SPARC open standard to work within, was to code the instruction set defined by this standard into a text-based description suitable for translation into an electronic circuit.

“Coding is performed using a hardware description language called VHDL which resembles a software programming language but has specific features to describe an electronic circuit,” Roland explained.

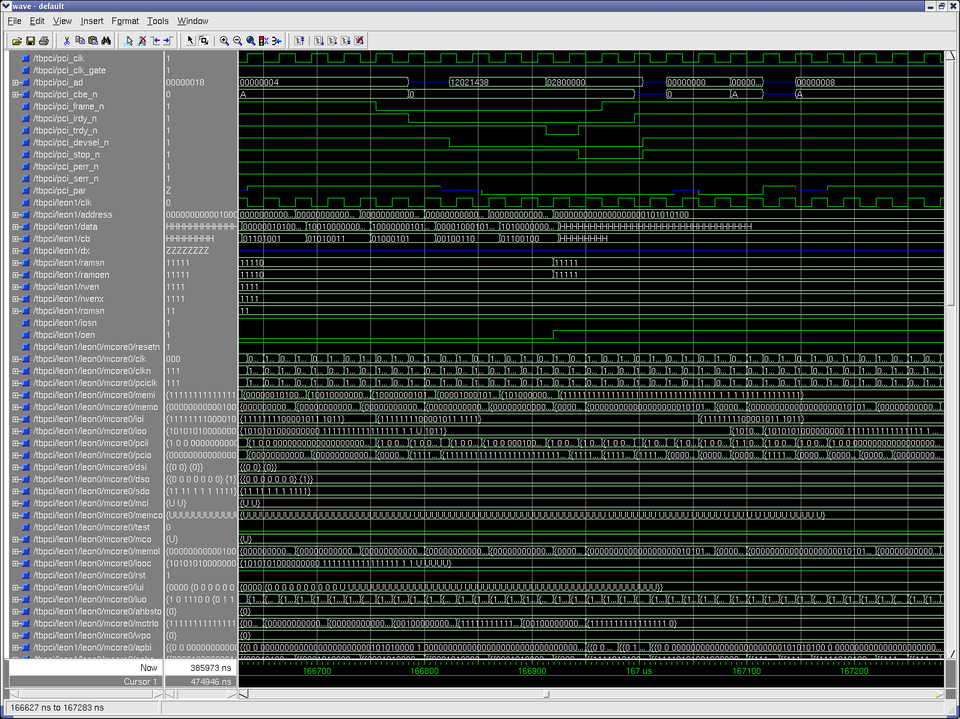

The resulting description contained several thousand lines of code: the LEON2-FT VHDL IP core. This VHDL code could then be simulated on computers, to validate it was operating as intended in advance of producing any hardware. A reduced version of the LEON IP core was distributed to the user community to obtain crowdsourced debugging tips.

“The next stage was then to physically translate that code to create a test board hosting a programmable chip called a ‘field programmable gate array’ (FPGA) where the LEON design could be put to work and tested.”

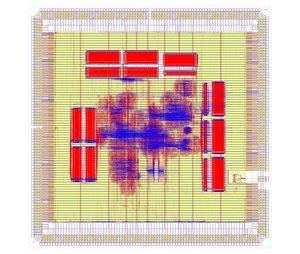

The reprogrammable nature of the FPGA allowed different design configurations to be evaluated before deciding on a definitive version for the final (and expensive) chip manufacturing, when the microprocessor design is etched onto semiconductor chips.

Into the nanoworld

Conservative space technology tends to lag behind its faster-moving terrestrial equivalent: the LEON2-FT is etched to a resolution of 180 nm, while the forthcoming Next Generation Microprocessor will go down to 90 nm or even 65 nm. For comparison, Intel’s latest CPU is around 32 nm.

These 90 nm and 65 nm technologies, while available in the commercial world for many years, are currently being validated for use in space through a pair of ESA activities called the Design Against Radiation Effects (DARE) and Deep Sub Micron (DSM) initiatives.

This descent into the nanoworld throws up fresh design challenges – such smaller technology is more sensitive to Single Event Upsets, for example – but success would mean that spacecraft designers can go on assuming enhanced processing performance for future missions for many years to come.