MIL-STD-1553 Testbench

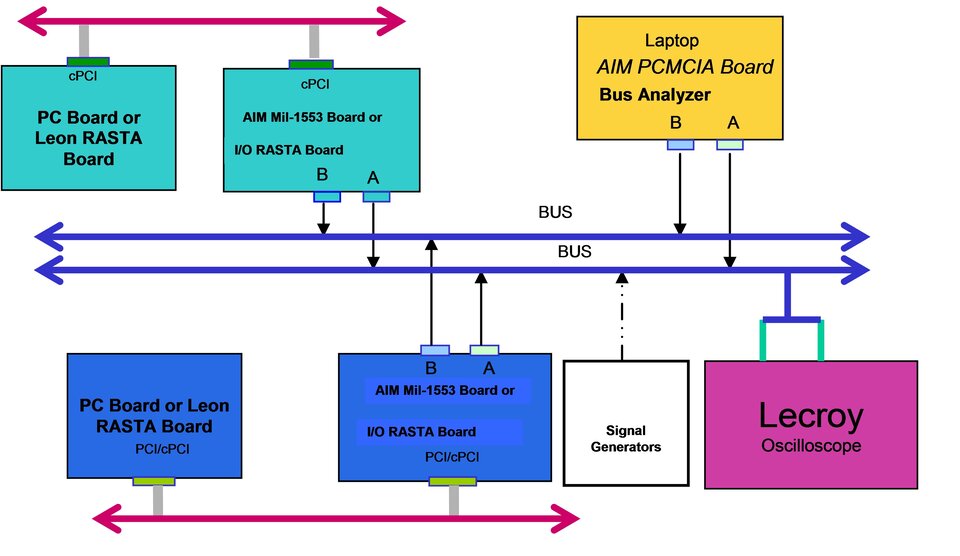

The Mil-1553 test-bed

The Mil-1553 test-bed in the Avionics Lab provides a facility for prototyping, simulation and verification of on-board bus protocols and services. The complete system includes hardware and software components: various processor boards (PC, ERC32, Leon), I/O boards, harness and software tools. All the layers of the protocols are covered, from the physical layer to the application layer.

Current capabilities:

- Record the Bus traffic and check for the CS, ME and correctness of CW DW SW response time and inter-message gap.

- Post analysis of the bus traffic.

- Complete set of harness which enables to emulate various configuration of the bus network. Possibility of discontinuities injection in the physical data bus.

- Prototyping at the level of ECSS-50-13C for PC and Leon board.

- Measure of signal margins (amplitude, rise and fall time, zero crossing etc...)

- Measure of noise impact, measure of BER

- Error Injection (Parity, Manchester, Bit and Word Count etc...)

- Any Instrument or a representative unit like bread board or Engineering Model can swap any simulated RT for testing in representative bus traffic.

Activities performed:

- Herschel/Planck Transfer Layer Protocol testing

- Prototype, simulate and verify the Satellite Data Bus Protocol (SDBP)

- Perform on-board equipment (units) I/F compatibility verification at SDBP level

- Check the requirements by detecting possible:

- Conflict between requirements

- Wrong and/or ambiguous requirements

- Missing requirements

- ECSS-E-50-13 Prototyping

- VEGA Physical Layer

Measurement of impact of nominal I/F activity on redundant I/F (noise).

- ERA project

Measurement of the signal integrity & electrical characteristics for the MMI EGSE Mil-1553 I/F.

Checking of bus traffic for CS and ME.