Analogue and Mixed-Signal IPs for Space

The functionality and performance of the satellites is heavily constrained by Mass, Size and Power. The development is in turn heavily constrained by Costs.

Technology downscaling has allowed to increase processing power of digital electronics, at relatively constant mass, size and power. Analogue circuits have to deal with increased data rates from the digital and the number of analogue interfaces, types and required accuracy in satellites is slowly rising. Unfortunately analogue circuits usually suffer from technology downscaling.

Taking the example of analogue-to-digital and digital-to-analogue converters, bandwidth can only be increased for converters at constant Mass, Size and Power consumption by reducing sensitivity. For increased sensitivity only integration offers the means to meet increased bandwidth at constant Mass and Size.

Consequently, new circuit designs and processes are required to increase performance and reduce the Power consumption.

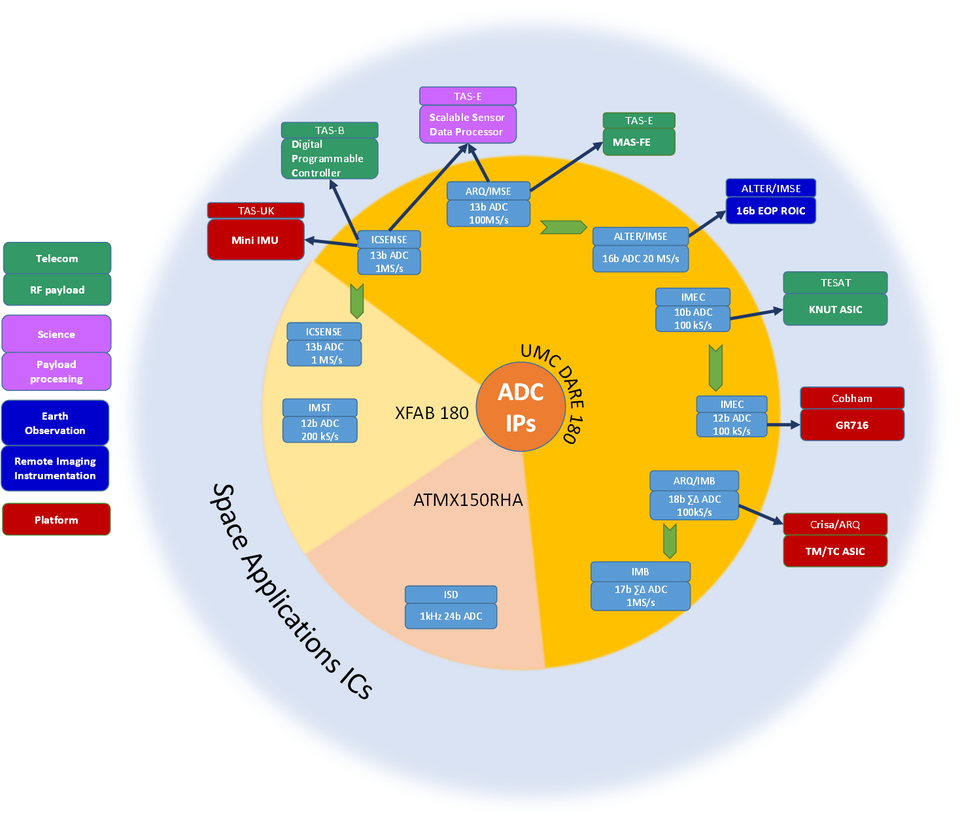

Analogue and Mixed-Signal IP-Cores are required to facilitate integration and keep development Cost within bounds. The availability of qualified IP mixed-signal blocks is also a key element to reduce development risk of integrated ASICs. Therefore, and in accordance to its mission “to provide and promote, for exclusively peaceful purposes, cooperation among European states in space research and technology and their space applications”, ESA is supporting from several years now the development and qualification of analogue and mixed-signal IPs, on various technologies, via several R&D programs (TRP, GSTP, ARTES…). Those IPs have been successfully integrated in space applications ICs, including as illustrated in the chart below, demonstrating the merits of such developments. Some details on space-grade microcontrollers integrating those analogue IPs can also be found here.

This section intends to provide a non-exhaustive catalogue of European mixed-signal IPs and ASICs for space, and to serve as a portal to European IP providers.

IPs are currently available in the following technologies:

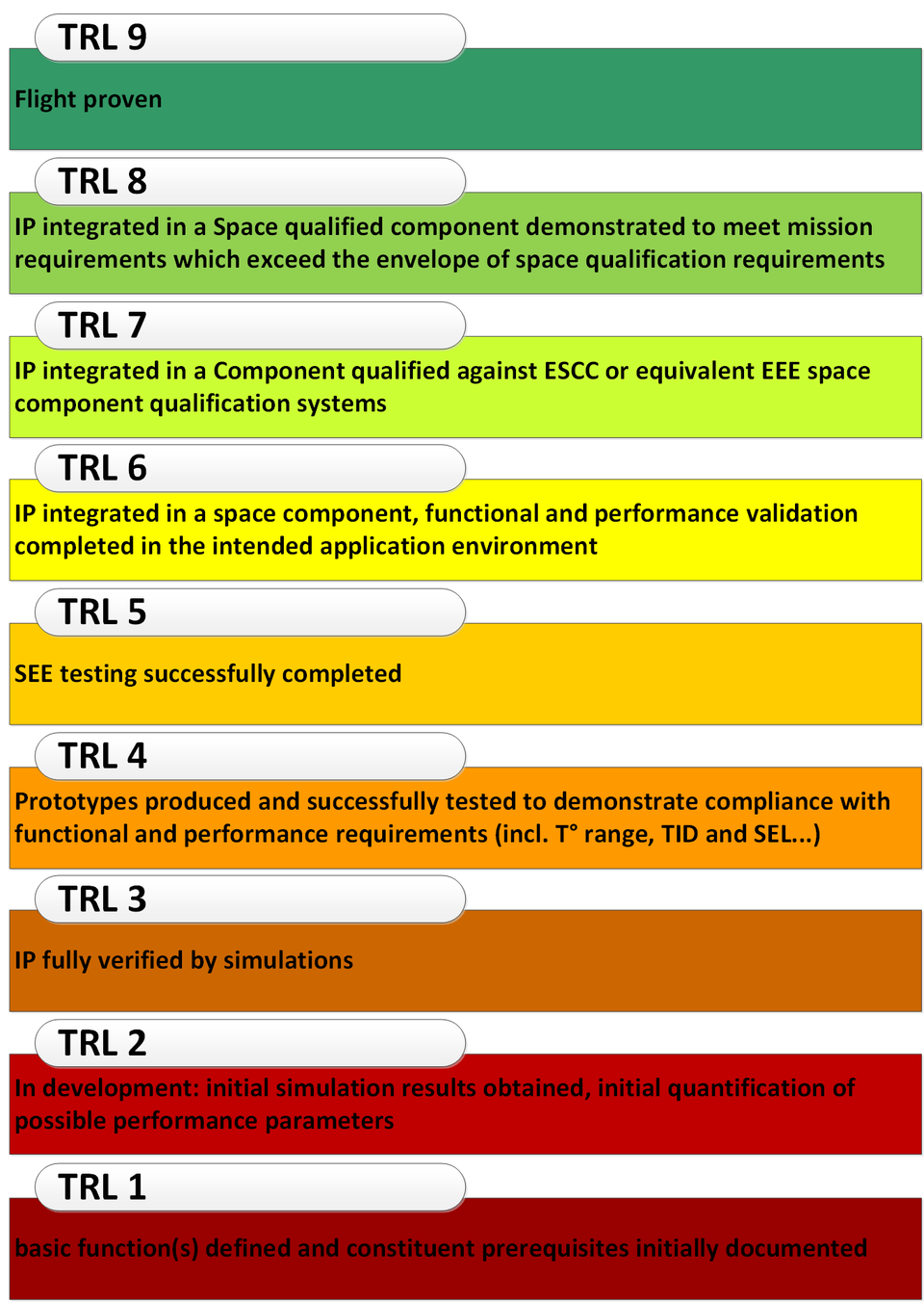

The IPs maturity is evaluated according to the TRL definition in the table below (ECSS-E-HB-11A).