SCCC IP Core

IP Core for medium data rate PDT, compliant with CCSDS 131.2-B-1 standard.

Overview

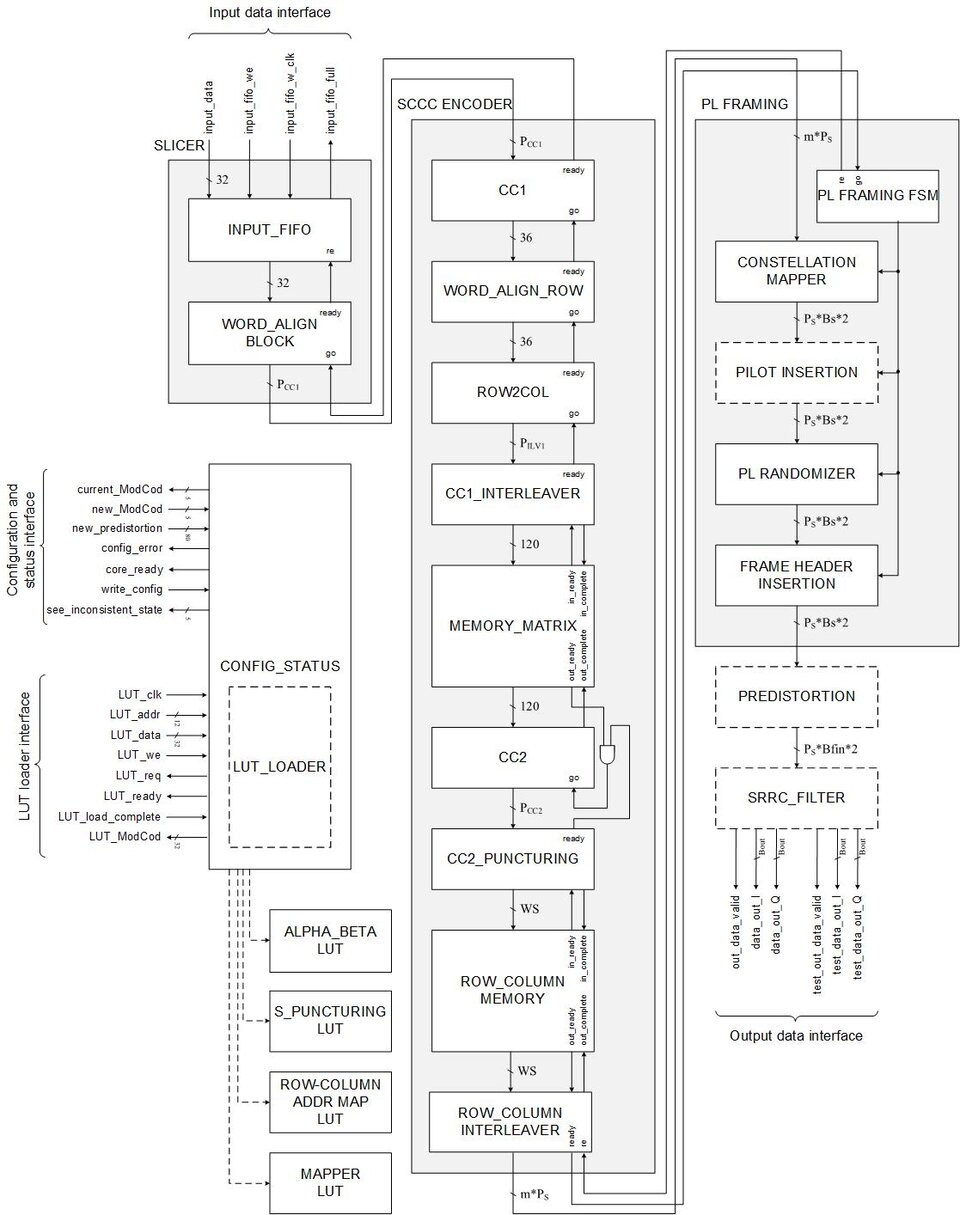

The IP Core for Medium Data Rate PDT implements a Serially Concatenated Convolutional Coding (SCCC) scheme for telemetry application, which functionality is compliant with CCSDS 131.2-B-1 (Flexible advanced coding and modulation scheme for high rate telemetry applications) standard. The transmitter makes use of a large variety of modulation schemes (including QPSK, 8-PSK, 16-APSK, 32-APSK and 64-APSK) and a wide range of coding rates.

Interfaces

The CCSDS Telemetry Transmitter IP core ports can be divided into the following interfaces, based on the functionality they are related to:

- Input data interface

- Output data interface

- Configuration and status interface

- LUT loader interface

- Clock, reset and enable

Configuration

The architecture was conceived with flexibility in mind. In order to easily adapt the IP core to many different use cases, it is provided with a complete set of hard configuration parameters, which allow enabling/disabling features of the processing, as well as optimizing the architecture in terms of performance/complexity trade-off. The hard configuration parameters are all accessible via the top-level generics.

Verification and validation

The IP Core has been extensively verified against a Matlab golden reference model. Validation was performed on RTG4 and BRAVE NG-MEDIUM development boards.

Technology mapping

The IP Core has been successfully mapped to the following target technologies:

- Microsemi RTAX2000

- Microsemi ProASIC RT 3000L

- Microsemi RTG4

- Xilinx Virtex5-QV

Current version

Release.

Developers

IngeniArs, 2018

Special licensing restrictions

None. The IP Core can be licensed to ESA Member States for ESA's own requirements.