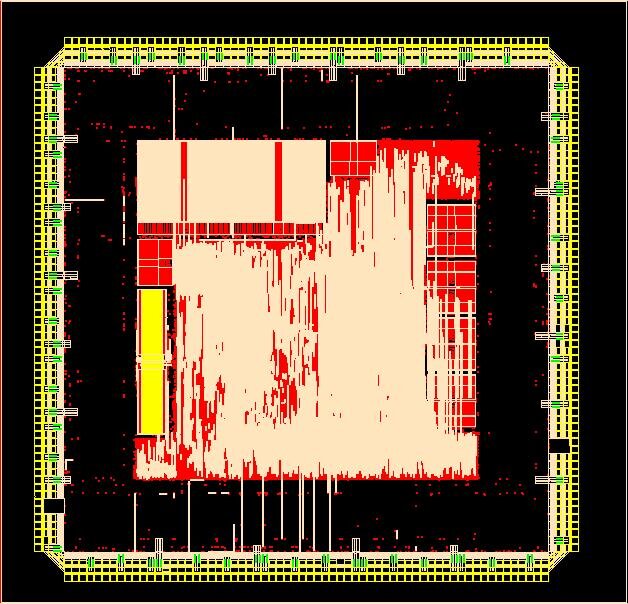

The LEONUMC Test-Chip Implementation

The version 1.0.4 of the LEON-FT model including the PCI interface has been implemented in UMC 0.18 um technology on a IMEC/Europractice MPW run. The design uses the commercial VST (Virtual Silicon Technologies) libraries, but implements full SEU-fault tolerance features provided by LEON-FT (EDACs, parity protection, TMR flip-flops with triplicated clocks).

The purpose of this development was on one hand to allow an evaluation of the UMC technology with the commercial libraries in radiation environment. Of course, no total dose immunity was to be expected, however SEU testing at ESTEC's Californium facilities have shown an excellent efficiency of the SEU mitigation mechanism implemented in the LEON-FT design: Many errors (including multiple) have been detected in the on-chip memories, but were all successfully corrected. No (multiple/uncorrectable) errors have been detected in the flip-flops. However, a 'latchup-like' behaviour has been observed during these tests, which shall be subject to further investigations.

A second objective was to provide an early prototype of the LEON-FT processor, which will be produced as a flight component (AT697F) by Atmel. LEONUMC is to a large extent functionally compatible with the future AT697F, and a development board allowing users to prototype their applications is available from Gaisler Research and Pender Electronic Design.