DRPM - Dynamically Reconfigurable Processing Module

In this ESA funded TRP project (22424/09/NL/LvH), hardware reconfigurable devices (FPGAs) for exploiting run-time adaptability and processing performance of payload processing systems are investigated. Therefore, a dynamic reconfigurable processing module (DRPM) demonstrator is developed, considering both hardware and software aspects, including a software design environment. The demonstrator is capable to exploit and unveil partial and dynamic reconfigurability of SRAM-based FPGAs for space applications. Besides meeting this basic challenge, the activity also develops advanced concepts for mitigating radiation effects. In the end, the DRPM demonstrator allows for exploiting novel and cost-efficient high performance processing concepts in payload processing systems.

Project Objectives

The mission of the activity is to investigate hardware reconfigurable devices (FPGAs) for exploiting run-time adaptability and processing performance of space systems. In particular, the payload system of satellites is targeted in the sense that benefits and challenges of integrating reconfigurable devices as (additional or compensating) units for on-board processing of payload systems are exploited. The objective is met by developing a DRPM demonstrator, which covers certain aspects of space missions. The demonstrator is capable to exploit and unveil the features given by modern FPGAs that offer partial and dynamic reconfigurability. A number of benchmark activities will be conducted therefore. The benchmarks will show the processing performance and flexibility offered by SRAM-based FPGAs. Both software and hardware aspects will be considered. Concerning the harsh space requirements and particularly due to the SRAM-based reconfiguration technology, mitigation of radiation effects and recovery in case of failure will be emphasized. A dedicated failure fault-tolerance and error correction unit is foreseen that provides techniques such as advanced scrubbing. Moreover, a software design environment based on an appropriate design flow is designed. The project will be finally concluded also in terms of requirements to migrate the DRPM demonstrator into a flight version.

Features

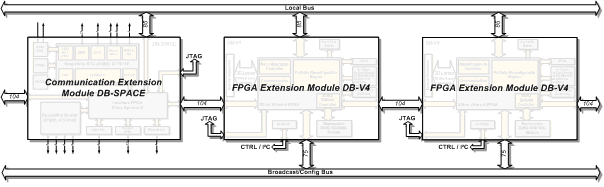

The DRPM manages one or more instruments via dedicated instrument interfaces, ranging from high rate instruments interfaced via WizardLink or lower rate instruments interfaced via CAN bus, discrete I/O or legacy serial links such as e.g. RS422. Instrument control may be performed according to an instrument’s specific needs, which may include control via SpaceWire, CAN bus or customized discrete interfaces. The DRPM interfaces the avionics through MIL-STD-1553B and may interface a mass memory module through SpaceWire. The DRPM contains a partially reconfigurable core that allows for customized interfaces to be tailored depending on specific needs. The main feature of the partially reconfigurable core, however, is to allow for high performance data processing algorithms to be implemented to cover a wide range of applications. In addition it supports in-flight reconfiguration during a mission if required, while being failure tolerant to space environment effects typically caused by high energy particles. The DRPM demonstrator is designed using the RAPTOR-X64 prototyping environment, which is developed at the University of Paderborn, Germany (www.raptor2000.de). The environment supports the acceleration of computationally intensive applications as well as partial dynamic reconfiguration. The RAPTOR system follows a modular approach, consisting of a base system and a variety of extension modules. During the course of this activity, the RAPTOR environment will be extended by a specific space module (DB-SPACE) that offers all relevant interfaces for comprehensive testing in laboratory environment. The space module connects to one or more FPGA modules (DB-V4) that comprise Xilinx Virtex 4 devices. Processing modules can be loaded onto the FPGAs on demand by partial and dynamic reconfiguration. Multiple modules may share the reconfigurable area at the same time. Modules may also request area on more than one FPGA if required. An intelligent system controlling enables the dynamic reconfiguration including failure correction mechanisms based on advanced scrubbing, redundancy and relocation techniques.

Project Plan

For the activity, ten tasks are executed, reasonably distributed into three phases, where based on analysis and design (phase 1), the manufacturing, test and validation (phase2), the DRPM shall be finally assessed by benchmarks (phase 3) and the guidelines for the migration to flight use shall be compiled (phase 3).

Key Issues

The DRPM project targets on exploiting dynamic and partial reconfiguration, which is given by certain FPGAs nowadays. Through dynamic and partial reconfiguration a processing in space and time can be realized. Despite being appealing in terms of performance, energy, re-use of processing area, etc., this technique imposes additional challenges both on hardware and software level. As the S-RAM based FPGAs required for dynamic reconfiguration are prone to radiation effects, the DRPM project targets mitigation techniques in a holistic approach. Built-in support of the FPGAs is intelligently combined with software-based monitoring and failure correction mechanisms.

DRPM Benefits

Generic reconfigurable module: The DRPM is a generic reconfigurable module, which fully exploits the reconfiguration capabilities of FPGAs, binging numerous advantages. In terms of system-specific hardware, a reconfigurable generic module can ensure maximum reuse of development across different systems. Moreover, a more modular and cost-efficient approach can be used with only custom modules being added as peripheral systems within the FPGA. High performance processing: Current and near future application specific standard products offer limited processing performance, which often require multiple device instances to support the high data rates provided by current instruments. In contrast, the FPGA-based DRPM inherently supports high data rate applications like image processing or software-defined radio. Compared to general purpose processors, FPGAs often offer a better performance, while they outrival ASICs in terms of adaptability. Fine tune payload processing based on instrument observations: The DRPM allows for changing or adapting payload processing during the flight mission. It can be freely adapted to scenarios, even if it was not foreseen at design time. Moreover, if the devices can be reconfigured dynamically, this adaptation can also be done during run-time. This allows for implementing time-sharing of the reconfigurable resources between different applications, thus increasing the area efficiency.

Current Status

Based on a comprehensive exploitation of suitable mission scenarios, operation phases, target applications and basic needs, as well as a holistic trade-off and survey of techniques and methods, the detailed requirements for the DRPM demonstrator could be formulated and specified. The project currently is in the phase of defining the architecture of the DRPM by embedding it into the RAPTOR prototyping environment. Foremost, the team designs a tailored extension module, which provides interfacing for space-specific requirements, such as SpaceWire, MIL-interfaces, etc. The Atmel AT7913E SpaceWire RTC is foreseen as system controller. Due to the maturity of the RAPTOR environment, a goal-oriented procedure can be followed, which also guarantees smooth finalization of the project, including high-quality results.

Contact

- Project Manager : Michael Ditze

- Postal Address : Bernhäuser Str. 40-42, 73765 Neuhausen, Germany

- Email : research @ twt-gmbh.de

- Phone : +49 (0) 7158 / 17 15-54

- Additional Contact : Florian Dittman

- Postal Address : Bernhäuser Str. 40-42, 73765 Neuhausen, Germany

- Email : research @ twt-gmbh.de

- Phone : +49 (0) 7158 / 17 15-54