Dynamically Reconfigurable Processing Module (DRPM)

Astrium Limited and IDA Technische Universität Braunschweig are developing a dynamically reconfigurable processing module (DRPM) using the latest SRAM-based FPGA technology. The DRPM is a generic design, suitable for a wide range of mission applications which require high capacity on-board processing. The ability to dynamically reconfigure all or part of the FPGA allows multiple applications to share a common hardware resource, which offers considerable advantages for the system designer and operationally for the instrument end user.

Project objectives

The project aim is to raise the TRL of on-board processing using reconfigurable SRAM-based FPGAs by building a technology demonstrator. The three main objectives are: (1) The specification, design and manufacture of a breadboard DRPM. The design is generic, applicable to a wide variety of mission payloads requiring high processing capacity, with the additional benefit of run-time full or partial reconfiguration. The breadboard uses commercial grade equivalents of flight qualifiable parts, with direct mapping to a rad-hard by design (RHBD) flight unit. The reconfigurable FPGAs are partitioned into user application areas which interface to IDA’s SoCWire network-on-chip in the static area of the FPGA. This ensures that partitions can be individually reconfigured without affecting the operation of other partitions. (2) Implementation of a prototype Application Development Environment (ADE), this being the set of processes and software tools which would be made available to application developers to build and test their instrument data processing applications which will run as user applications on the DRPM. (3) Use of the prototype ADE to develop a set of benchmarks, selected to be representative of typical payload processing applications, and then to quantify the breadboard performance through a series on benchmarking tests.

Features

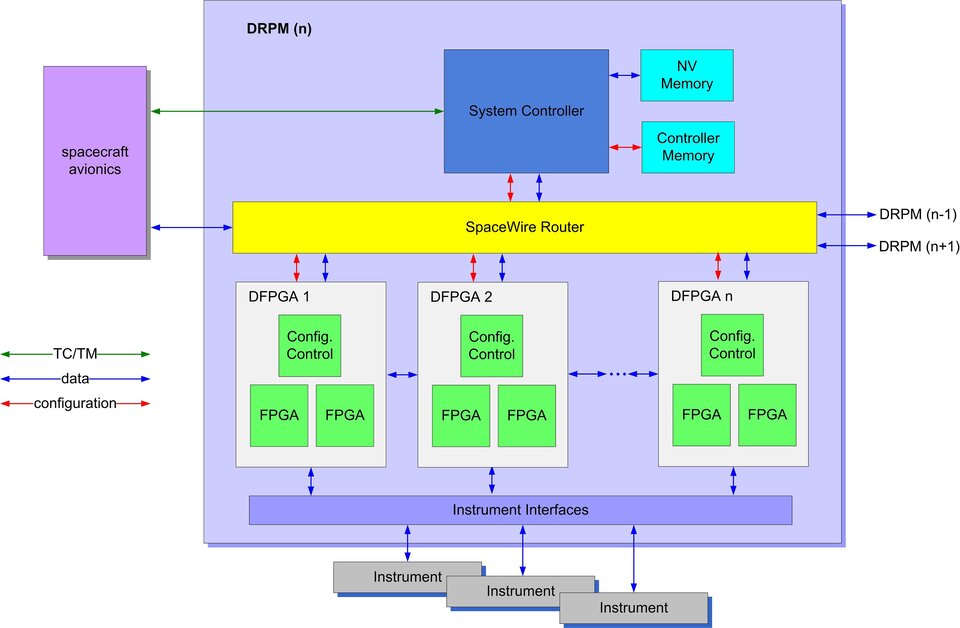

The DRPM is based on a reconfigurable block (DFPGA), comprising two reconfigurable FPGAs (RFPGAs), working memory (SDRAM) and a local configuration controller which manages the configurations and the SEU susceptibilities of the RFPGAs (e.g. configuration scrubbing). Multiple DFPGAs are combined as required to form the DRPM. Module management is performed in the System Controller, with a SpaceWire network providing the intra-Module links between the System controller and the DFPGAs, and external links to instruments, payload mass memory, and other DRPMs (if present). The RFPGA can be fully or partially reconfigured according to the instrument operational mode. Partial reconfiguration involves RFPGA spatial partitioning so that multiple processes can operate on it independently. Glitch free partial reconfiguration is assured because partitions use SoCWire to connect to a SoCWire router fixed in the RFPGA static logic. Since SoCWire is based on the SpaceWire standard, the SoCWire and SpaceWire systems effectively operate as one network. The system management software is distributed between the System Controller and Configuration Controller(s) CPUs. The System Controller handles TM/TC processing, mode management, network configuration, integrity monitoring, and overall management of reconfiguration and user applications. The Configuration Controller performs local reconfiguration and integrity testing on command, RFPGA scrubbing (where required) and supports the software component of user applications. In the demonstrator the System Controller is implemented on Gaisler’s SpW RTC development card with a custom card for additional memory. The router is the Star Dundee SpaceWire-USB card which for flight would be replaced with the AT7910 SpaceWire Router. The DFPGA is a custom card, with the configuration controller implemented in the Actel proASIC A3PE3000 (RTAX 2000/4000 for flight) and the RFPGAs are from the Xilinx Virtex 4 or 5 family (XQR4VSX55-XQR5VFX130 for flight).

Project plan

The Project has three phases. Phase 1 (9 months) is system requirements analysis, demonstrator and ADE specification and design. Phase 2 (9 months) is demonstrator hardware, firmware and software manufacture followed by integration and validation. Phase 3 (6 months) is performance testing using benchmark applications developed with the prototype ADE. Astrium Ltd is responsible for system design, ADE design, high level on-board software and benchmark applications. IDA is responsible for demonstrator hardware and firmware and low level software, and the test system hardware and software. The demonstrator and ADE will be delivered to ESTEC at the end of the project.

Key issues

The key issues which are being addressed in this project are:

- demonstration of run-time, partial reconfiguration of SRAM based FPGAs in a payload processing context

- implementation of an SEU tolerant payload architecture using FPGA scrubbing and reconfiguration, as the basis for a rad-hard by design (RHBD) flight unit

- performance measurement using suitably designed benchmark applications to validate the hardware and software architecture of the DRPM and to indentify areas where performance could be improved

- design and implement a prototype Application Development Environment for instrument application and system developers

Expected main benefits

A payload processor with reconfigurable hardware offers many system level advantages due to its ability to support planned, mode-dependent functional alterations as well as unplanned updates. In-flight reconfigurable digital hardware enables multiple independent modes to be time multiplexed on the same processing resource, allowing the hardware to be sized for the maximum operational load, rather than for the aggregate of every function, with attendant savings in mass, power and design complexity. Further, in-flight reconfiguration allows run-time tailoring of the quality of service (e.g. by switching between lossy and lossless compression algorithms). Operationally, there is the major system advantage that the initial hardware functions loaded at launch may subsequently be updated or complemented with new configurations. This may be due to changing operational requirements, improved processing algorithms, or in response to in-flight calibration or sensor hardware faults. Indeed, the ability to flexibly reconfigure in response to faults offers the possibility to move away from the traditional, mass penalising, prime/redundant paradigm.

Current status

Phase 1 of the development has been completed with a CDR held at ESTEC in October 2010. Phase 2 which commits to hardware manufacture has started. Initial integration of the demonstrator is scheduled for the end Q1 2011.

Contact

- Project Manager: Alex Wishart

- Postal Address: Astrium, Gunnels Wood Road, Stevenage, Herts. England SG1 2AS

- Email: alex.wishart * astrium.eads.net

Phone: +44(0)1438 77 4475

- Additional Contact: Jørgen Ilstad

- Postal Address: European Space Agency ESTEC- Keplerlaan 1 P.O Box 299 - 2200 AG Noordwijk ZH - The Netherlands

Email: Jorgen.Ilstad * esa.int

replace * with @