IP Cores

The ever increasing complexity of today’s systems, and integration levels of today’s ICs, has made design reuse an essential part of the design process. The main concept of design reuse is to utilise already developed, tested and verified building blocks to build more complex systems, rather than developing these functions from scratch in every new design. The benefits are shorter development times, faster time to market, and easier verification, among others. Furthermore, since the functions implemented by the reused blocks have already been verified, they can –ideally- be used as “black box” components, so the end user of these blocks only needs to look at the interfaces of these blocks, without having to worry too much about the details of how the required functionality was implemented internally.

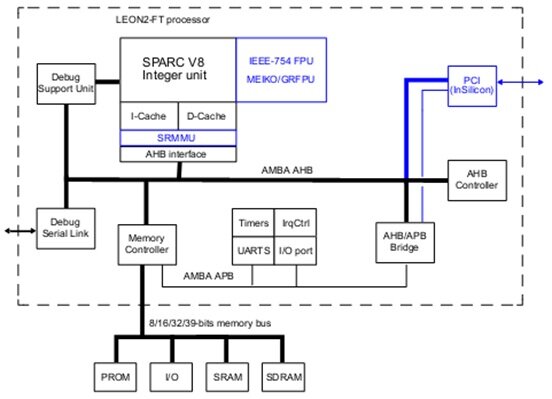

These reusable designs are often referred to as “Intellectual Property Cores” or “IP cores”, and they are an essential part of all complex Systems on Chip (SoC). ESA maintains a portfolio of such IP cores, implementing functions commonly used in integrated circuits targeting space applications, such as on-board interfaces (CAN, 1553, SpaceWire), packet telemetry and telecommand CODECs, and even a full fault tolerant 32-bit RISC microprocessor (LEON2-FT). These are licensed to the European space industry for use in ESA projects or other space-related developments. More information on the ESA IP cores portfolio can be found on the ESA IP Cores website.