Leading up to LEON: ESA’s first microprocessors

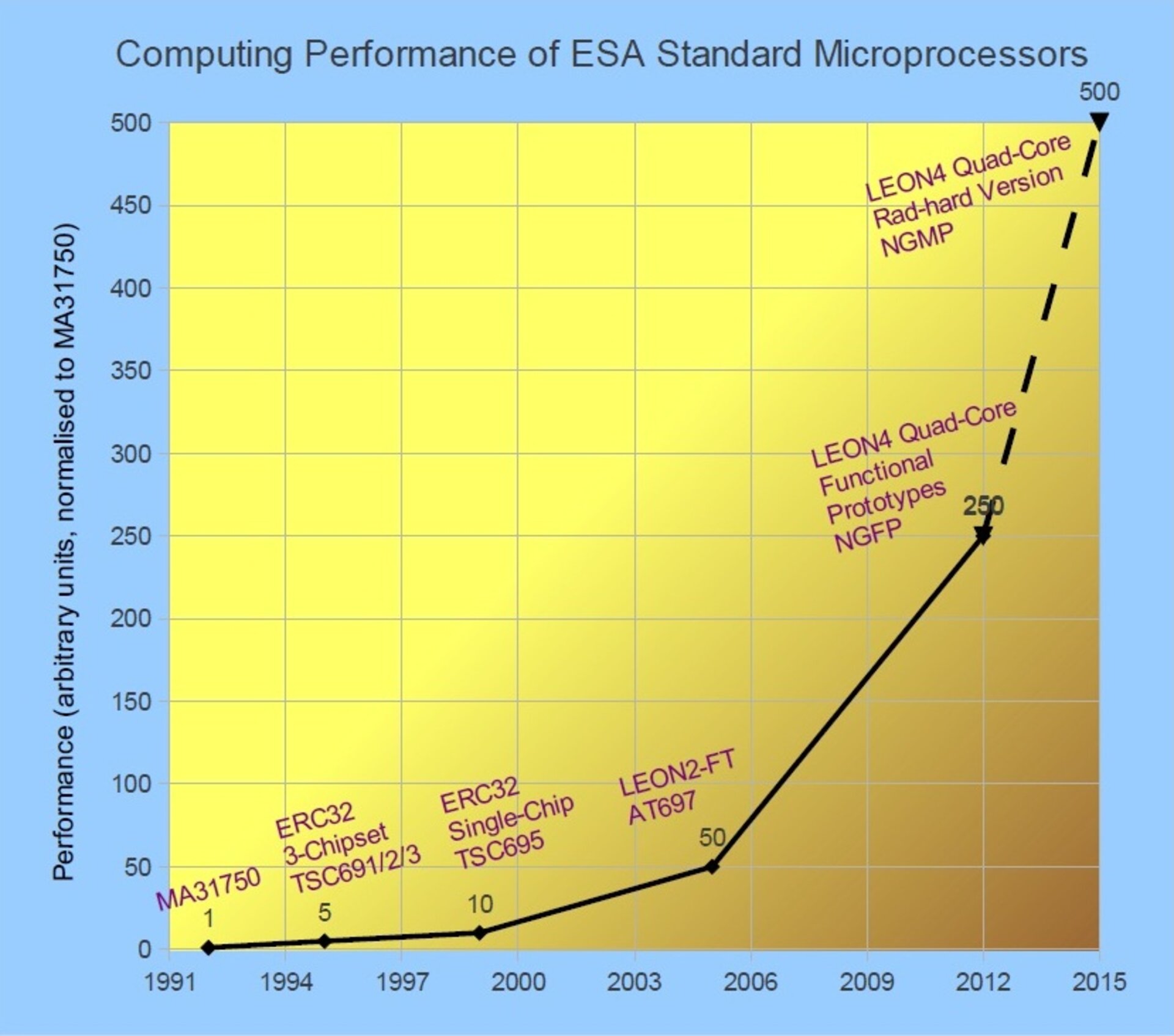

ESA engineers began by taking existing designs and adapting them for space use. This process began with the Agency’s MA31750 16-bit microprocessor, designed in the early 1990s.

Manufactured in the UK, this microprocessor is sold internationally and still in widespread use in the satellite telecommunications sector, as well as serving ESA missions, including comet-chaser Rosetta.

For its next attempt the Agency adopted the SPARC (Scalable Processor Architecture) open industry standard, resulting in the ERC32 design.

An initial three-chip set (each chip containing part of the microprocessor) was developed in the mid-1990s. Commercialised by Atmel as the TSC691/692/693, it was employed by several computers of the International Space Station, by the Automated Transfer Vehicle supply truck and by ESA’s highly automated Proba-1 Earth observation microsatellite.

Its second generation, developed in the late 1990s, merged these three chips into one: the ERC32 ‘single chip’, subsequently commercialised by Atmel as the TSC695. This product has been at the heart of European space systems for more than a decade.

Notable adopters include the inertial units guiding the flight of Ariane 5 launchers and the Herschel and Planck space observatories, among other ESA science missions.

“About 3500 ERC32 single-chip flight units have been sold, and it remains on sale to this day, valued in the space industry as a mature, reliable product,” Roland added.

Starting over

Then, for ERC32’s follow-on microprocessor came the concept of starting over from scratch.

“The idea in the second half of the 1990s was not just to rely on this existing SPARC open architecture but to take full control of the functionality, which meant making our own design,” explained Roland.

Development of the LEON microprocessor was initiated by two then ESA staff André Pouponnot and Jiri Gaisler, in coordination with their division head, Richard Creasey.

Not that the small ESA team did everything themselves: by initially releasing a reduced version of the LEON design as open source code to a worldwide community of users, including many universities, they crowdsourced valuable debugging feedback ahead of manufacturing (for more information, see the link: LEON: The making of a microprocessor for space).

Boasting a five-fold performance improvement on the ERC-32, ESA’s LEON2-FT is once more manufactured by Atmel. Features are etched onto its underlying semiconductor at 180 nanometre scale, compared to the single-chip ERC32’s 500 nm. The smaller the scale, of course, the more computing power can be crammed onto an individual chip.

To give an idea of scale, an individual atom measures a few nanometres across while a typical human hair is about 60 000 nm to 100 000 nm wide. Manufacturing at such a scale sounds impressive but the commercial semiconductor industry is typically operating several generations ahead of the space industry.

(Continued in: LEON's first flights).