Reprogrammable FPGAs demonstrate potential of multi functionality

A GSTP activity together with Topic Embedded Products, Netherlands, has found that through partial reconfiguration of field-programmable gate array’s (FPGA) it can reduce costs and at the same time increase the functionality of control and data processing applications in space.

FPGAs are versatile hardware components whose functionality changes depending on their configuration. Currently, reprogrammable FPGAs can change configuration more than one time: affecting the whole FPGA or only to part of it (total or partial configuration), and either only at power-up (static) or during ‘run-time’ (dynamic). This activity targeted the most ambitious case: dynamic partial reconfiguration

Topic Embedded has previously developed DYPLO – a software platform that helps developers to change the functions in an FPGA during run-time. DYPLO enables this re-use of FPGA resources in space. But to realise this, the DYPLO technology first needed to be transformed into a space qualified platform.

The activity hoped to reduce costs in two ways. Firstly, by re-using hardware for different functionalities just by changing the programming then less hardware needs to be developed and built. Secondly, the relative ease of programming when using the DYPLO framework means quickly changing the functions of the chips in the hardware is more feasible than ever.

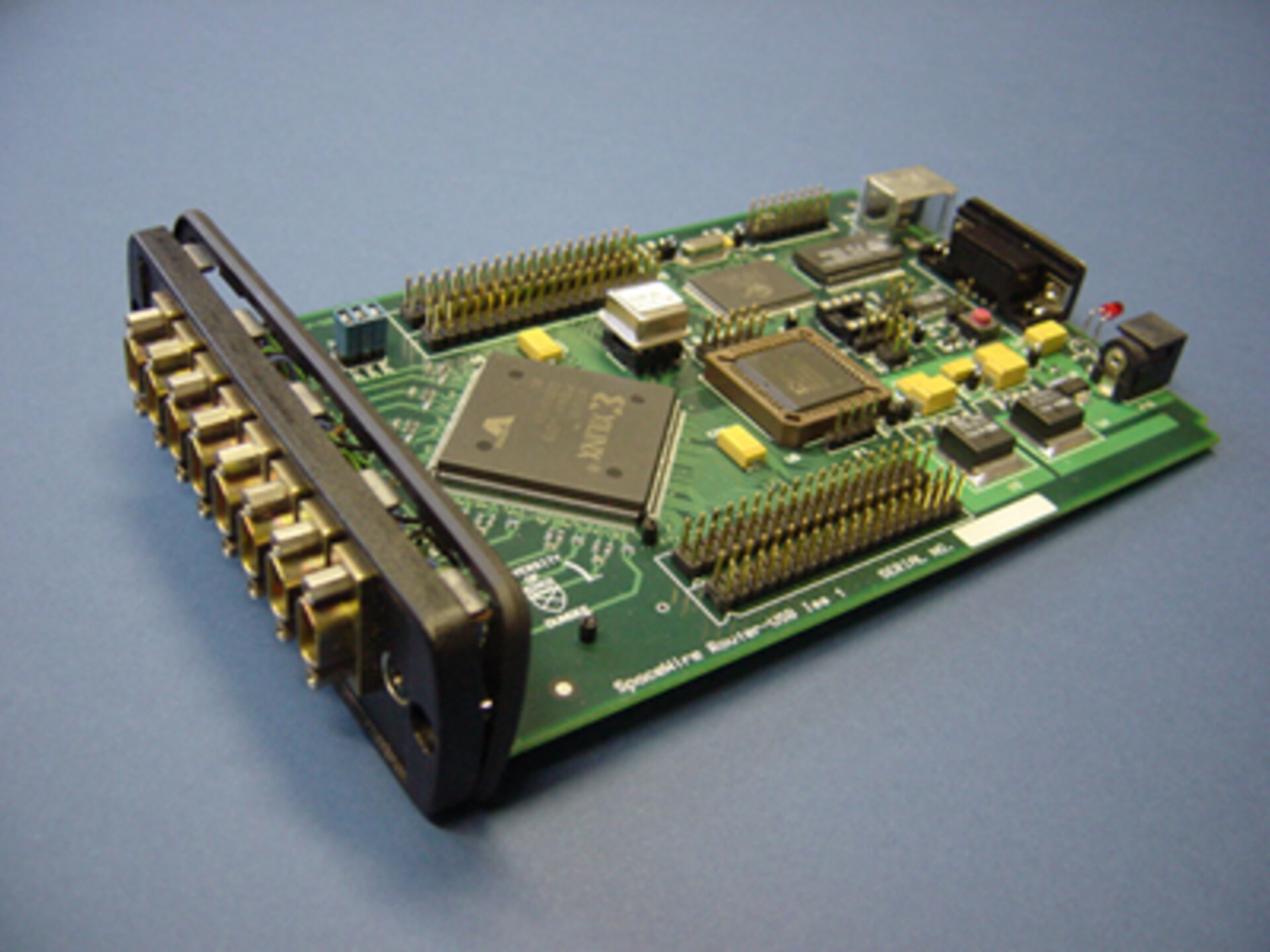

This activity demonstrated DYPLO on a platform that contains an FPGA also available as a space-hardened version. To demonstrate the use of DYPLO on the new platform, an application was developed based on the algorithms from the ESSR (European Space Software Repository).

The activity found that DYPLO offers easy use of run-time partial reconfiguration on FPGAs, ultimately enabling re-use of FPGAs for different purposes at different phases in flight. Besides that, DYPLO allows for the full integration of FPGA development and software development into a single environment. This opens the use of FPGA technology for software developers in a more natural way of working, and could extend to support the European re-programmable BRAVE FPGAs.