Microprocessors

Microprocessors are a core component of modern electronics and on-board computers do not escape this rule. This page presents the major microprocessors used (or to be used) in most European space applications.

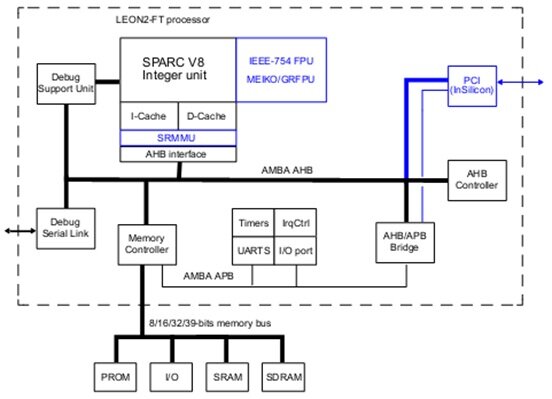

LEON2 / LEON2-FT

The LEON2 is a synthesisable VHDL model of a 32-bit processor conforming to the IEEE-1754 (SPARC V8) architecture. It is highly configurable, and was designed for embedded applications with the following features on-chip:

- 5-stage integer pipeline

- separate instruction and data caches

- hardware multiplier and divider

- memory management unit

- interrupt controller

- debug support unit with trace buffer

- two 24-bit timers

- two UARTs

- power-down function

- watchdog

- 16-bit I/O port

- Flexible memory controller

The LEON2 is based on an AMBA AHB/APB bus architecture, so new modules can easily be added to extend its functionality. The processor can be implemented in both FPGA and ASIC technologies.

The LEON2-FT design is an extension of the basic LEON2 model including advanced fault-tolerance features to withstand arbitrary single-event upset (SEU) errors without loss of data. The fault-tolerance is provided at design (VHDL) level, and does not require an SEU-hard semiconductor process, nor a custom cell library or special back-end tools. Atmel has manufactured an ASIC version of the LEON2-FT in the ATH18RHA rad hard process, available through their catalogue as part number AT697F. The AT697F is qualified according to QML-Q.

Availability:

The LEON2-FT VHDL IP core is available from ESA directly, under special licensing conditions. Please refer to the LEON2-FT IP Core webpage on the ESA IP Cores website for more information on licensing the LEON2-FT model.

The LEON2 (non-FT) model is no longer maintained. It is superceded by LEON2-FT, and the subsequently released LEON models (LEON3, LEON4).

The ASIC implementation of the LEON2-FT is available from Atmel,as part number AT697F.

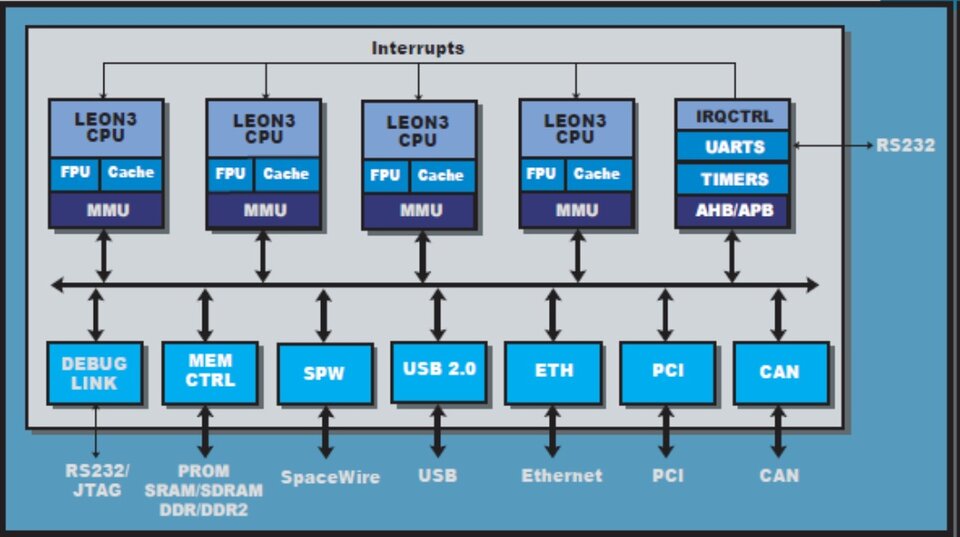

LEON3 / LEON3-FT

The LEON3 is a synthesisable VHDL model of a 32-bit processor compliant with the IEEE-1754 (SPARC V8) architecture. The LEON3 is an extension to the LEON2 processor, featuring a 7-stage pipeline (vs the 5-stage pipeline of the LEON2), and supporting both asymmetric and symmetric multiprocessing (AMP/SMP). Up to 16 CPU can be used in a multiprocessing configuration. The LEON3 model is highly configurable, and suitable for System-on-Chip (SoC) designs. It features the following:

- SPARC V8 instruction set with V8e extensions

- Advanced 7-stage pipeline

- Hardware multiply, divide and MAC units

- High-performance, fully pipelined IEEE-754 FPU

- Separate instruction and data cache (Harvard architecture) with snooping

- Configurable caches: 1 - 4 ways, 1 - 256 Kbytes/way. Random, LRR or LRU replacement

- Local instruction and data scratch pad RAM, 1 - 512 Kbytes

- SPARC Reference MMU (SRMMU) with configurable TLB

- AMBA-2.0 AHB bus interface

- Advanced on-chip debug support with instruction and data trace buffer

- Symmetric Multi-processor support (SMP)

- Power-down mode and clock gating

- Robust and fully synchronous single-edge clock design

- Up to 125 MHz in FPGA and 400 MHz on 0.13 um ASIC technologies

- Extensively configurable

- Large range of software tools: compilers, kernels, simulators and debug monitors

- High Performance: 1.4 DMIPS/MHz, 1.8 CoreMark/MHz (gcc -4.1.2)

The LEON3-FT design is a fault-tolerant and SEU-proof version of the LEON3, suitable for space applications. As in the LEON2-FT model, the fault-tolerance is provided at design (VHDL) level, and does not require an SEU-hard semiconductor process, nor a custom cell library or special back-end tools. The LEON3-FT model features most of the functionality of the LEON3 processor, and also includes the following fault-tolerance features:

- Register file SEU error-correction of up to 4 errors per 32-bit word

- Cache memory error-correction of up to 4 errors per tag or 32-bit word

- Autonomous and software transparent error handling

- No timing or performance impact due to error detection and correction

The following features of the standard LEON3 processor are NOT supported by LEON3FT:

- Local scratch pad RAM (I and D)

- Cache locking

- LRR cache replacement algorithm

The LEON3/LEON3-FT models were developed, and are currently distributed, by Aeroflex Gaisler. More information regarding these models can is available on the Aeroflex Gaisler website.

Availability:

The LEON3/LEON3-FT IP cores are available in source code (VHDL) or netlist format from Aeroflex Gaisler. The LEON3-FT is also available in the following ASIC/FPGA implementations:

Aeroflex Gaisler

- Device : GR712RC Dual-Core SOC

- Frequency: 100 MHz

- Performance: 250 DMIPS

Aeroflex Colorado Springs

- Device: UT699 Single-Core SOC

- Frequency: 66 MHz

- Performance: 75 DMIPS

Aeroflex Gaisler / Actel

- Device: LEON3FT-RTAX

- Frequency: 25 MHz

- Performance: 20 DMIPS

Heritage: (TBD)

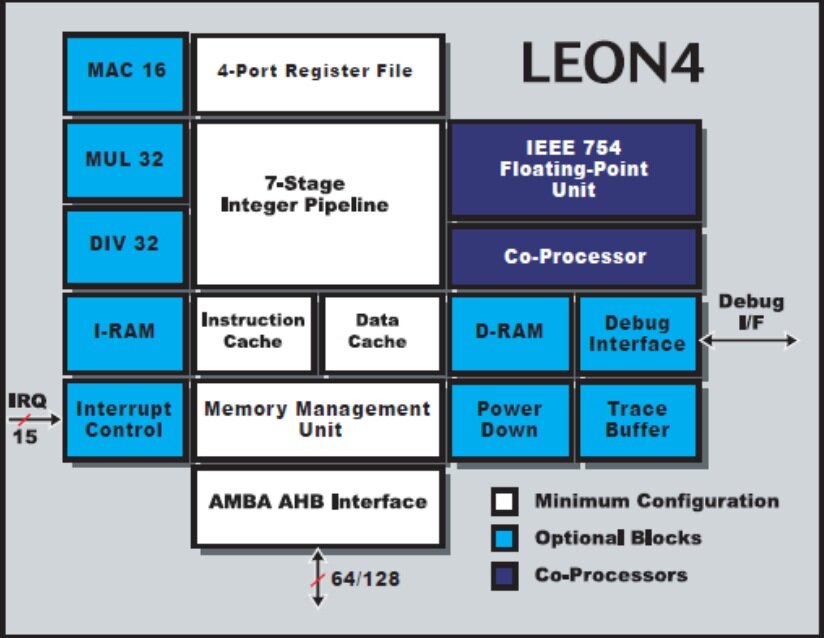

LEON4 / LEON4-FT

The LEON4 is the latest implementation of the SPARC V8 architecture by Aeroflex Gaisler, in the form of a synthesizable VHDL model of a 32-bit microprocessor. As was the case with the previous LEON models, the LEON4 is also highly configurable, and particularly suitable for system-on-chip (SoC) designs. The LEON4 extends the LEON3 model with support for an optional Level-2 (L2) cache, a pipeline with 64-bit internal load/store data paths, and an AMBA interface of either 64- or 128-bits. Branch prediction, 1-cycle load latency and a 32x32 multiplier results in a performance of 1.7 DMIPS/MHz, or 2.1 CoreMark/MHz.

The LEON4 processor has the following features:

- SPARC V8 instruction set with V8e extensions

- Advanced 7-stage pipeline, with branch prediction

- 64-bit single-clock load/store operation

- 64-bit 4-port register file

- Hardware multiply, divide and MAC units

- High-performance, fully pipelined IEEE-754 FPU

- Separate instruction and data L1 cache (Harvard architecture) with snooping

- Configurable caches L1: 1 - 4 ways, 1 - 256 kbytes/way. Random, LRR or LRU replacement

- Configurable L2 cache: 256-bit internal, 1-4 ways, 16 Kbyte - 8 Mbyte

- SPARC Reference MMU (SRMMU) with configurable TLB

- AMBA-2.0 AHB bus interface, 64- or 128-bit wide

- Advanced on-chip debug support with instruction and data trace buffer, and performance counter

- Symmetric Multi-processor support (SMP)

- Power-down mode and clock gating

- Robust and fully synchronous single-edge clock design

- Up to 150 MHz in FPGA and 1500 MHz on 32 nm ASIC technologies

- Extensively configurable

- Large range of software tools: compilers, kernels, simulators and debug monitors

- High performance: 1.7 DMIPS/MHz, 2.1 CoreMark/MHz, 0.35 SPECint2000/MHz

Availability:

The LEON4 IP core is available in source code (VHDL) or netlist format from Aeroflex Gaisler. A LEON4 SoC ASIC has also been implemented in eASIC 90nm Nextreme1 technology. More details on the availability of the LEON4 ASIC can be obtained by Aeroflex Gaisler directly.

Heritage: (TBD)

ERC32

ERC32 is a radiation-tolerant SPARC V7 processor developed for space applications. Two versions have been manufactured by TEMIC (now Atmel), the ERC32 (3-) Chip Set, and the ERC32 Single Chip. More details on these chips can be found on the ESTEC ERC32 webpage.

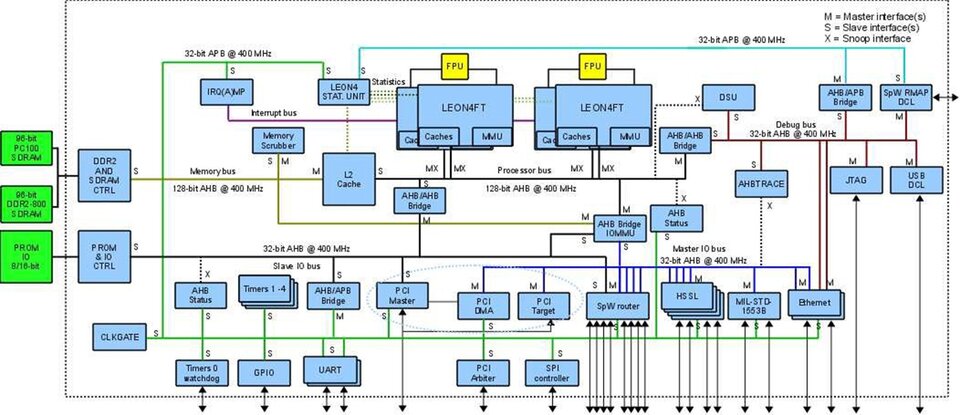

NGMP

The Next Generation Multipurpose Processor (NGMP) is a fault tolerant multiprocessor system-on-a-chip (SoC), based on the LEON4 core. It is currently (as per February 2012) being developed by Aeroflex Gaisler in an activity initiated by ESTEC/ESA.

The NGMP has the following on-chip functions:

- 4x LEON4 SPARC V8 processor cores with MMU and two shared GRFPU floating-point units

- Level-2 cache, 4-ways, BCH protection, supports locking of 1-4 ways

- Debug Support Unit (DSU) with instruction and AHB trace buffers

- USB, Ethernet, JTAG and SpaceWire debug communication links

- 64-bit DDR2-800 SDRAM memory controller with Reed-Solomon EDAC

- 64-bit PC100 SDRAM memory controller with Reed-Solomon EDAC

- Hardware memory scrubber

- 8/16-bit PROM/IO controller with BCH EDAC

- I/O Memory Management Unit (IOMMU) with support for six groups of DMA units

- 8-port SpaceWire router/switch with four on-chip AMBA ports with RMAP

- 2x 10/100/1000 Mbit Ethernet MAC

- 32-bit 33/66 MHz PCI master/target interface with DMA engine and arbiter

- MIL-STD-1553B interface controller

- 2x UART

- SPI master/slave controller

- Interrupt controller with extended support for asymmetric multiprocessing

- 1x Timer core with five timers and watchdog functionality

- 4x Timer core with four timers

- Separate AHB and PCI trace buffers

- Clock gating unit

- LEON4 statistics unit (performance counters)

- AHB status registers

More information on the NGMP development, and its current status, can be found on the ESA NGMP webpage.