Electronic System-Level Design Methodology

Systems-on-Chip (SoCs), and in particular Multi-Processor SoCs (MPSoCs) are complex systems, requiring particular design methodologies; with respect to traditional hardware architectures, the main issues can be listed as: (a) need for higher-levels specifications, (b) reduced time-to-market, (c) increased verification complexity, (d) huge design space, (e) highly complex software development, and (f) need for methodologies enabling concurrent design of hardware/software.

Tackling Design Complexity

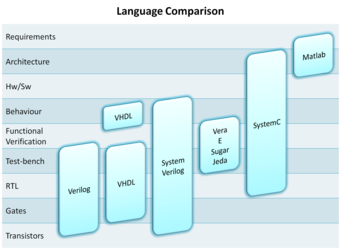

As first promising solution to tackle the design complexity, the International Technology Roadmap for Semiconductors (ITRS) lists the use of high-level abstractions (grouped under the name Electronic System Level) during the system specification and during its preliminary design phases.

Various techniques and methodologies are being devised; among them, Hardware/Software co-design is of particular interest as MPSoCs are, by their nature, processor-centric and thus software-centric. Larger and larger portions of current applications are being implemented in software and their development starts dominating the cost of the whole system, hence becoming critical for the system’s release schedule. The concurrent design of hardware and software aims indeed at mitigating these issues, allowing software to be developed before the final hardware is ready.

Use of ESL at the European Space Agency

The European Space Agency is promoting the development and the use of Electronic System Level design methodologies and tools to simplify the production of future On-Board Computers and to analyze and, eventually, optimize the ones currently in use.

In particular, there are various on-going activities aimed at implementing a coherent design flow at the Electronic-System abstraction Level, providing the possibility of performing effective Hardware/Software co-design. Such activities are centered on:

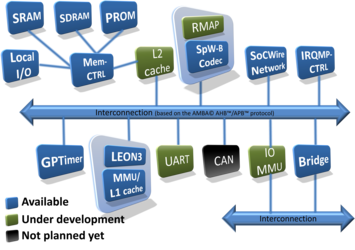

- High-Level models of the VHDL IP-cores used on LEON-based Systems-on-Chip are being developed using the IEEE SystemC and IEEE TLM standards and related libraries as developed by Accellera.

- High-Level model of the LEON processor, for standalone use (i.e. as an emulator for software development) or to integrate with other IP models.

- The Virtual Platform (VP) technology will be used for the runtime management of the IP models, and of the simulation in general.