SpW-RMAP-Dundee

The SpaceWire-RMAP IP core implements the Remote Memory Access Protocol (RMAP) extensions to SpaceWire. RMAP provides a standard mechanism for reading from, and writing to memory in a remote SpaceWire node. It allows users to readily implement the RMAP protocols in FPGAs and ASICs.

Overview

There are two main function types of the RMAP IP core. The first type is referred to as the Initiator RMAP interface, which sends out RMAP commands and receives any replies. The second type is the Target RMAP Interface, which receives RMAP commands, executes them and sends out any required replies. The RMAP IP core also includes the SpaceWire-b CODEC IP block which handles the SpaceWire protocol point to point link.

The RMAP IP core target and initiator function is illustrated in the following diagram (click on thumbnail to enlarge).

RMAP packets are initiated in the initiator user logic, encoded as RMAP packets in the “Initiator RMAP Interface”, sent over the SpaceWire link as an RMAP packet, decoded by the “Target RMAP Interface” and data or information is passed to the target user logic after authorisation of the command. The “Target RMAP Interface” formats an RMAP reply packet which is sent over the SpaceWire interface, decoded by the “Initiator RMAP Interface” and the reply data/information is passed to the initiator user logic. The IP core can be configured to be target only, initiator only or both.

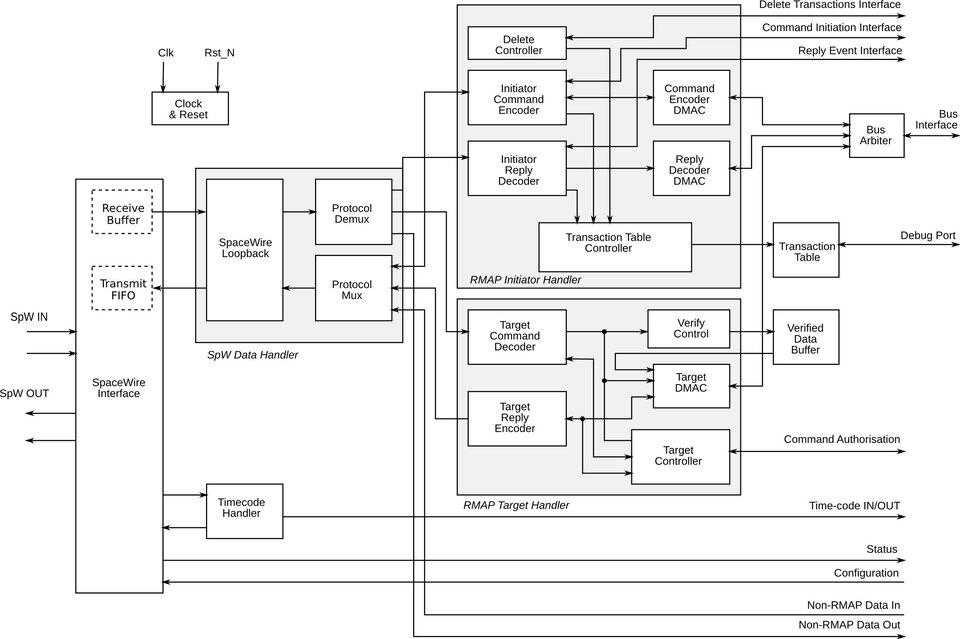

The architecture of the RMAP core is illustrated in the following diagram (click on thumbnail to enlarge).

The SpaceWire CODEC implements the SpaceWire serial point to point protocol and provides FIFO ports to the Protocol Input and Output blocks. The protocol input and output blocks determine the destination of packets dependent on the packet header. The Target units decode RMAP command packets, read or write data from the host bus and return RMAP reply packets. The initiator units accept commands into the transaction table, encode RMAP command packets, decode reply RMAP packets and output status information. Target and initiator units interact with the user memory space using DMA controllers, one for each unit to increase memory access performance.

- Memory Interface

The RMAP controller interface to memory is modelled on the AMBA AHB bus standard which provides a pipelined control/data bus transfer model. Data is transferred to and from the bus in bursts using internal burst FIFOs in the RMAP core. The bus can be configured for different bus size widths, byte order and bit swapping operations.

- Configuration

The RMAP core is highly configurable using generics at the top level of the RTL port. The configuration options of the core are listed below.

• Target only, Initiator Only, Target and Initiator

• Host bus width, burst transfer depth, byte/bit order

• Watchdog timer on bus transfers

• Initiator maximum commands, transaction table size

• Internal FIFO sizes, verify buffers size

Area/Speed Results

The core is generic RTL code which can be synthesized for a range of ASIC and FPGA technologies including Actel and Xilinx FPGAs.

The core has been implemented at 200 Mbps in a Xilinx Spartan3E device and currently at 100 Mbps in an Actel AX2000 (with no optimization). The results are obtained using the Mentor Graphics Precision toolkit (version 2008a.39).

Spartan-3E 1600 (slices)

- Core : 3196 (22%)

- Initiator : 2306 (16%)

- Target : 1134 ( 8%)

Actel AX2000 (modules)

- Core : 11184 (35%)

- Initiator : 7824 (25%)

- Target : 4464 (14%)

Actel ProASIC3E 1500 (tiles)

- Core : 11397 (30%)

- Initiator : 8088 (22%)

- Target : 4576 (12%)

The distribution package for the SpaceWire-RMAP IP core also includes an application note describing the implementation of the RMAP IP core in a Xilinx Spartan-3 FPGA. The application note includes documentation, testbench and test software, as well as the complete design database.

Developers

Chris McClements, University of Dundee, 2009

Martin Dunstan, University of Dundee, 2009-06-17

Current Release

version 1, June-2009

Special licensing restrictions

ESA can grant licenses for the use of the SpaceWire-RMAP IP core only for activities funded by the Agency (ESA projects).

The SpaceWire-RMAP IP core also includes the SpaceWire-b IP core, which incorporates the IEEE 1355 High Performance Serial Bus Std (Data/Strobe interface) patented by STMicroelectronics. Therefore an appropriate STMicroelectronics patent notice must be included in the licenses and the final products.