SpW-RMAP-Astrium

The SpaceWire-RMAP IP core implements the Remote Memory Access Protocol (RMAP) extensions to SpaceWire. RMAP provides a standard mechanism for reading from, and writing to memory in a remote SpaceWire node. It allows users to readily implement the RMAP protocols in FPGAs and ASICs. This IP-Core is an extension of the SpaceWire-AMBA IP-Core and was originally developed in the frame of the SCOC3 System-on-Chip.

Overview

This SpaceWire-RMAP IP-Core performs the Spacewire RMAP function as defined in the ECSS-E-50-11 Draft F, September 2006. With respect to final RMAP standard (number ECSS-E-ST-50-52), this IP-Core does not support the Reply Address field (described in Section 5.1.6 of document ECSS-E-ST-50-52).

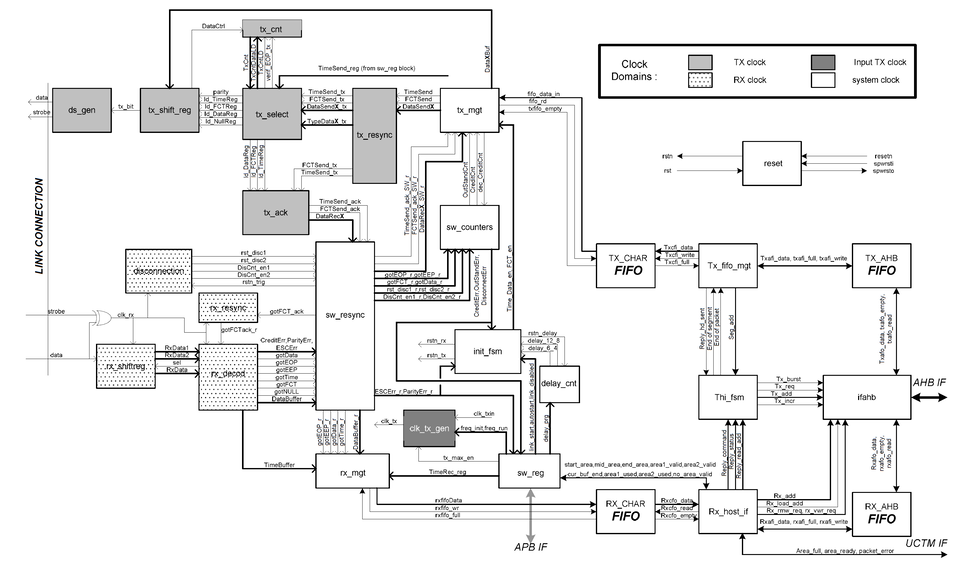

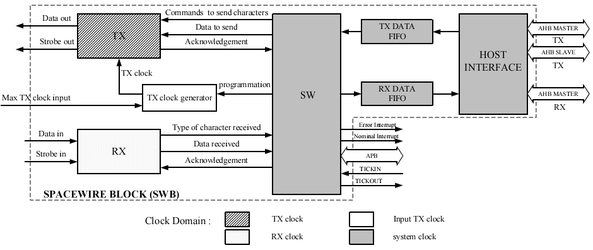

As shown in the Figure below, the IP-Core features AMBA AHB and AMBA APB interfaces for the communication with the host SoC; the external communication interface is, of course, compliant to the SpaceWire protocol.

Area and Speed Results

The core is generic RTL code which can be synthesized for a range of ASIC and FPGA technologies including Actel and Xilinx FPGAs. Examples of resource usage on some Xilinx technologies is given below; note that no significant effort was spent in trying to optimize those results. The SpaceWire link speed reached by both of those implementations is 200Mbps.

Virtex 4QV – XQR4VLX200:

Number of Used Slices: 2994 (12%)

Number of Used Slice FFs: 2174 (4%)

Number of Used 4 inputs LUTs: 5547 (11%)

Virtex 5Q – XQ5VFX130T:

Number of Used Slice Registers: 2155 (2%)

Number of Used Slice LUTs: 4217 (5%)

Developers

Astrium - Tam Le Ngoc, Marc Soury - 2008

Licensing Conditions

No special licensing conditions apply. For more information refer to the ESA IP-Cores licensing page.