Space Wire node interface IP core

| Programme: | TRP Workplan | Achieved TRL: | 3 |

| Reference: | T701-305ED | Closure: | 2016 |

| Contractor(s): | TELETEL SA (GR), Airbus DS (FR), Thales Alenia Space (FR) | ||

The various SpaceWire IP’s offered by ESA's IP core service are widely used in many ESA projects and typically implemented in rad-hard FPGAs part of either instruments or the onboard data handling system.

Other important functions of a SpaceWire interface such as time synchronisation, configuration port and hardware support for specific protocols have still to be designed by the user, which requires significant effort to develop and validate.

Henceforth, the goal is to develop an easily configurable SpW Node IP core that reduces the need for in-depth knowledge of SpaceWire protocols in order to implement required functions in a standard compliant way.

Objectives

To develop an Intellectual Property core (IP-core) for a complete SpaceWire node interface in order to facilitate easier SpW node implementation in ESA projects.

Achievements and status

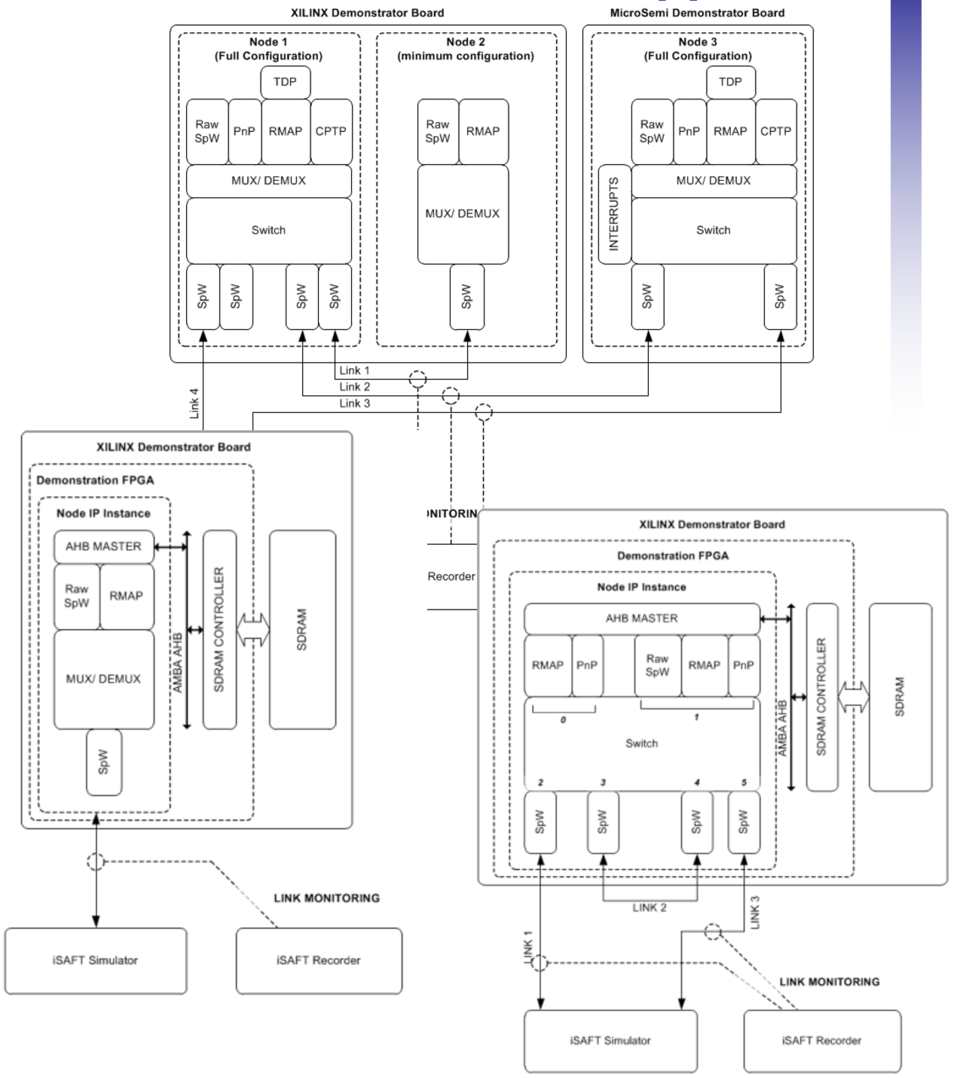

The various protocol engines have been implemented and proved functional: Configurable SpaceWire node IP core, which integrates a number of existing IP cores like the SpaceWire codec, Remote Access Memory Protocol (RMAP) IP core, SpaceWire-D (target) and Network Discovery Protocol support, SpaceWire switch; Parameters like the number of SpaceWire links, the level of support for the different protocols in hardware and the type of on chip interface are easily configurable for every instantiation of this IP core. Full code coverage verification is the next step, which due to the large number of configuration options is a significant task.

Benefits

Thanks to the development of the highly configurable IP core, it much simpler to implement a tailor-made complex SpW node implementations in e.g. payload instrument interfaces.

Next steps

To perform a complete code coverage verification of the IP-core and to optimize the design to require less FPGA resources.