Father of the chips steering Europe’s space missions

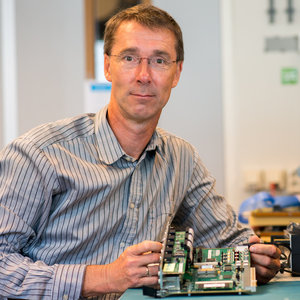

With every innovation there comes the moment it is put to the test. For space engineer Jiri Gaisler that was the day his brainchild was taken to a Belgian particle accelerator and exposed to a beam of high-energy radiation.

That occurred back in 2000, with the very first prototype of the LEON family of microprocessors, especially designed to work in space.

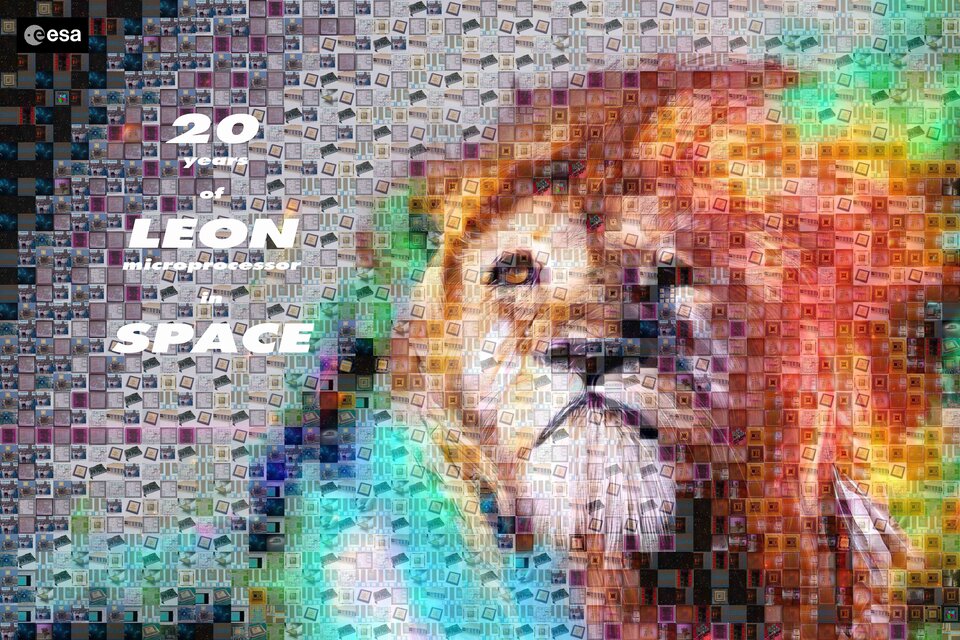

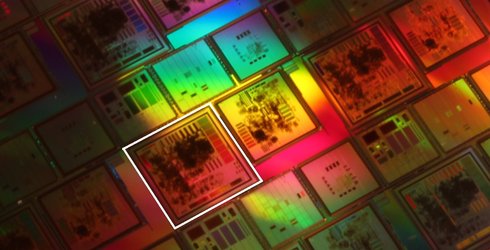

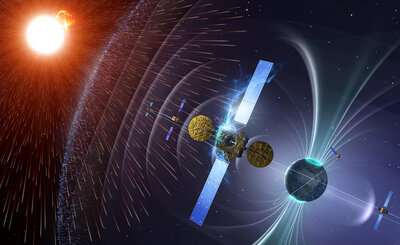

The test was a success: today there are thousands of LEON chips in place aboard European – and global – missions. Labyrinths of microcircuitry etched onto silicon chips, they are the source of embedded intelligence for key subsystems as well as the satellite platforms themselves.

First within ESA’s On-board Computers section, then later from the helm of his own company, Czechoslovakia-born, Swedish-raised Jiri worked alongside numerous collaborators within the Agency and multiple European companies to shepherd the LEON microprocessor from initial concept to its current commercial success.

“There are many microprocessors inside a typical satellite,” he explains. “They form the brain of the mission, with the software running on them performing all the main controlling functions, from payload operations to power management to communications with the ground.

“They’re as essential to European non-dependence in space as our own launchers, if not more so.

“When I started at ESA in the late 1980s we were developing our first 16-bit European microprocessors, the first generation of which was licensed directly from a US manufacturer, then the second generation we worked on our own: the MA31750, still available commercially to this day, and serving the Rosetta comet mission, for example.

“But looking forward we would need something more powerful; this was something of a golden age for ESA, with lots of new projects coming up: European contributions to the International Space Station, the proposed Hermes space plane and what became the Envisat environmental satellite.

“We needed to develop a new 32-bit processor, but didn’t have enough money to develop our own architecture. I remember visiting various Silicon Valley companies to look into licensing some existing design.

“In the end we decided to harness an open industry standard called SPARC (Scalable Processor Architecture), developed by Sun Microsystems but made freely available – this was the time of the CPU wars, with many different architectures coming out, and everyone promoting their own.”

Selecting SPARC to produce the resultant ERC-32 chip was a fateful decision, because it meant ESA escaped being locked into any proprietary design or architecture.

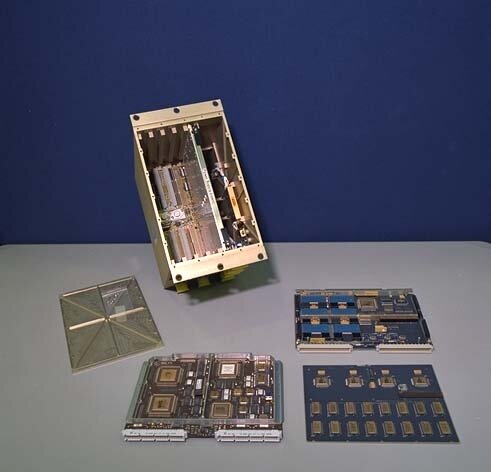

The ERC-32 – initially a three chip design, subsequently modified into a single chip – was developed from existing design templates. The result is still overseeing the ISS to this day, along with the inertial units of Ariane 5 launchers, among other high-profile missions.

“By the mid-90s the ERC-32 project was finished, but we were still receiving project requests for higher processing performance still,” Jiri recalls. “So we got together with industry partners and thought about how to proceed.

“One idea was to shrink down the ERC-32 still further, but instead I proposed we design our own processor core, again based on SPARC since it was an open standard we were familiar with.

“It was a risky decision at the time, just an idea on a piece of paper, but it was the path that led to the LEON.

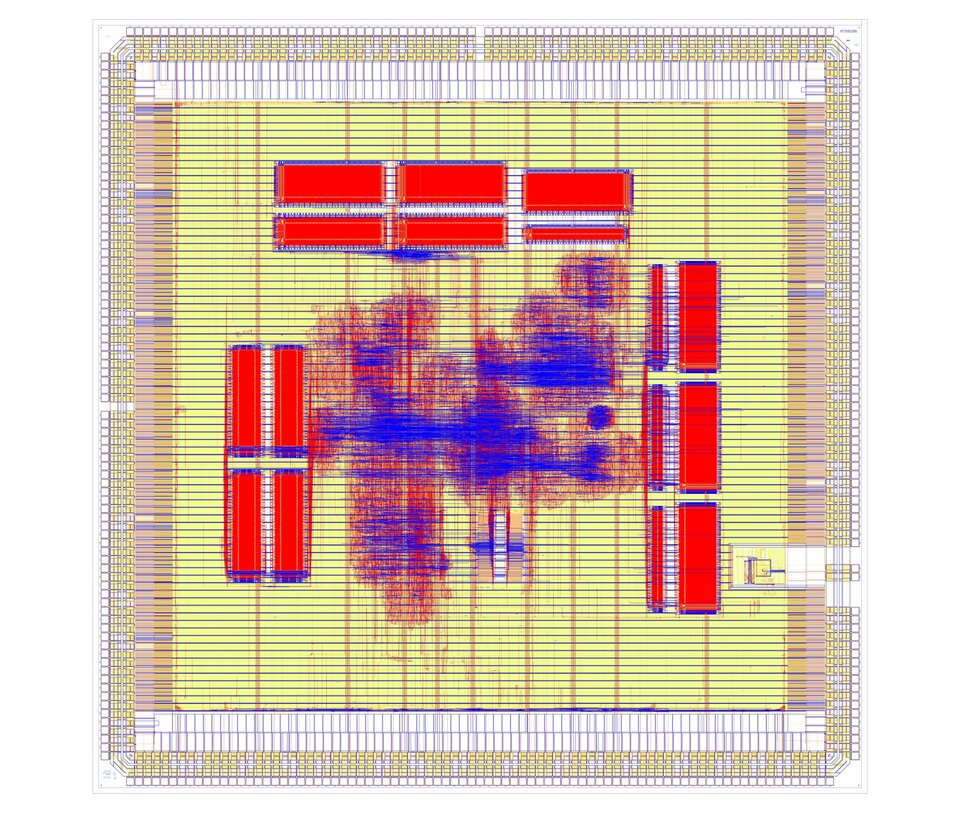

“The advantage was we could design from scratch around our specific space requirements: chiefly ‘fault tolerance’ against space radiation.

“As microprocessors shrink in scale they grow more powerful, but also more susceptible to the effects of charged particles from the Sun or deep space, leading to memory ‘bit flips’. Our idea was not to prevent such errors but to detect and remove them in hardware without letting the software know – so software writers wouldn’t have to take account of them.

“This is done by designing the microarchitecture pipeline to incorporate redundancy and error detection – including multiple parallel calculations able to vote on any ambiguous results. The challenge was to do this without unduly impacting the performance, speed and power consumption.”

It seemed to work in theory, but the LEON-1’s actual trial by radiation came around four years after designing it, at the Cyclotron Research Centre in Louvain-la-Neuve.

“We had different chips run in parallel on the same board, with one monitoring the others to detect when an error wasn’t handled,” explains Jiri. “It turned out very well, with 99.8% more correction capability.”

While LEON1 was a prototype, LEON2 went into production at Atmel in France, commercialised as the AT697. Jiri meanwhile left ESA, to begin a PhD back in Sweden. But he continued to consult on LEON development, and finally set up his own company, known today as Cobham Gaisler.

While ESA retained ownership of the LEON2-FT – the fault tolerant flight version of the LEON, Jiri’s company went to develop other LEON versions, starting with the resdesigned LEON3 and the current LEON4, the basis of ESA’s quadcore Next Generation Microprocessor, with prototypes now undergoing testing.

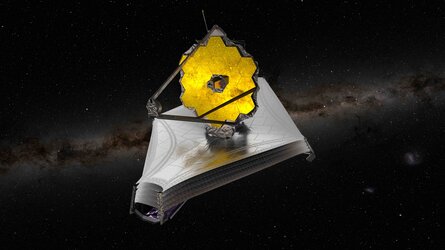

LEON2-FT microprocessors meanwhile began to reach space – steering the dive of ESA’s Intermediate eXperimental Vehicle spaceplane, running the startrackers and GPS receivers of Europe’s Sentinel family of Earth observers, overseeing the Gaia star mapper and the imminent BepiColombo mission to Mercury.

“There’s a lot of LEONS out there – and, more broadly, every European space mission runs on a SPARC microprocessor,” says Jiri. “What we achieved by relying on this open architecture, maintained by a separate organisation, is keep the instruction set stable for a very long time – more than 25 years – which is important because space projects typically have long lifetimes. And we’ve kept this stability without having to pay additional royalties or license fees and so on.”

Jiri has today retired from Cobham Gaisler, but recently returned to ESA’s technical centre in the Netherlands to mark two decades since the LEON was first designed.

“I didn’t set out to design microprocessors just because I like them, it was what was needed to be done,” concludes Jiri.

“But it’s a tremendous feeling to know all those long days and nights at my desk resulted in something that so many people and projects depend on, extending out into the Solar System.”

Germany

Germany

Austria

Austria

Belgium

Belgium

Denmark

Denmark

Spain

Spain

Estonia

Estonia

Finland

Finland

France

France

Greece

Greece

Hungary

Hungary

Ireland

Ireland

Italy

Italy

Luxembourg

Luxembourg

Norway

Norway

The Netherlands

The Netherlands

Poland

Poland

Portugal

Portugal

Czechia

Czechia

Romania

Romania

United Kingdom

United Kingdom

Slovenia

Slovenia

Sweden

Sweden

Switzerland

Switzerland