SHyLoC IP Core

SHyLoC comprises the VHDL description of two synthesizable IP cores that implement lossless data compression algorithms as defined by the CCSDS 123.0-B-1 and CCSDS 121.0-B-2 standards. Such IPs are capable of working independently, as well as jointly. In the latter case, the CCSDS-123 IP works as a pre-processor and the CCSDS-121 performs the entropy coding stage. The designed IP cores are technology independent and can be mapped to several FPGA targets representative of space-grade hardware.

The CCSDS lossless compression standards

High data rate multispectral and hyperspectral sensors and the limitations of the on-board storage and bandwidth make on-board data reduction mandatory. The Consultative Committee for Space Data Systems (CCSDS), has issued two lossless standards for satellite data compression:

- CCSDS 121.0-B-2: defines an entropy coder that utilizes Rice coding technique to encode blocks of one-dimensional data.

- CCSDS 123.0-B-1: focuses on three-dimensional images (multispectral or hyperspectral) and consists of a pre-processor that removes redundancies among samples in a three-dimensional neighbourhood and a subsequent entropy coding stage. Such entropy coding stage can be accomplished by the Rice coder defined in the CCSDS 121.0-B-2.

These two lossless standards are capable of reducing the data volume by removing redundancies in the data source, in such a way that the exact original data can be recovered after decompression.

Overview of the SHyLoC IP cores

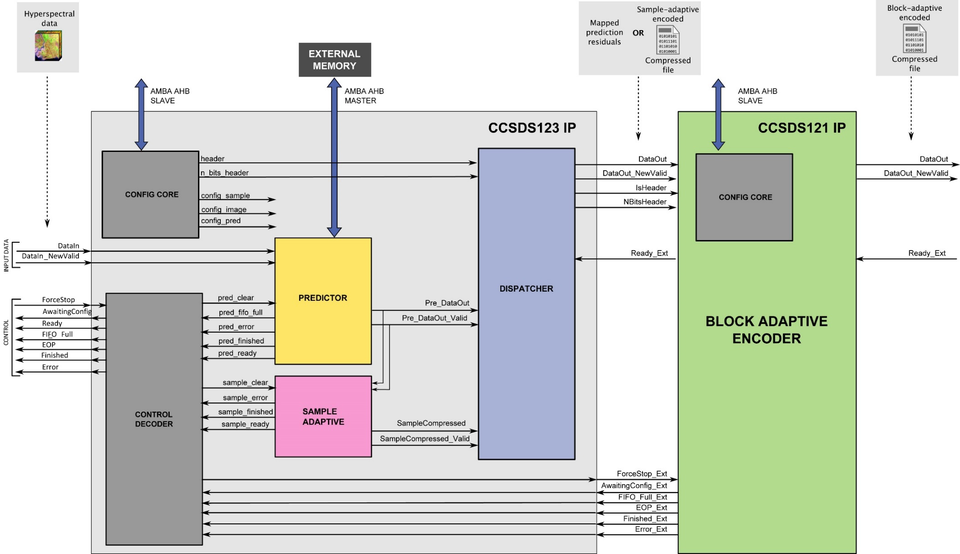

SHyLoC consists of two IP cores: the CCSDS-121 and the CCSDS-123, which are described in VHDL.

CCSDS-123 IP main features:

- High performance lossless compression of multispectral and hyperspectral data.

- Supports BSQ, BIP and BIL sample order.

- High throughput (up to 140 MSamples/s when implemented on a Virtex5 FX130)

- Can be used as external pre-processor (predictor) for the CCSDS-121 IP core.

CCSDS-121 IP main features:

- Universal lossless compressor based on Rice's coding.

- High throughput (up to 118 MSamples/s when implemented on a Virtex5 FX130).

- Can be used as external entropy coder for the CCSDS-123 IP.

Interfaces

The CCSDS-121 and the CCSDS-123 IP Cores have compatible interfaces, including input and output data interfaces, an AHB slave interface for configuration and a control interface to inform about the status of the compression.

When the IPs are working together, the output data interface of the CCSDS-123 IP core is connected to the input data interface of the CCSDS-121. The CCSDS-123 IP core includes an additional control interface that is meant to be connected to the control interface of the CCSDS-121 IP core.

Since the CCSDS-123 predictor needs to store a fair amount of intermediate values during the compression, an AHB master interface is included to allow the storage of these samples in an external memory.

Configuration

The IP Cores are fully configurable, reflecting the versatility of the standards. Configuration at compile-time is implemented by means of VHDL generic constants. The constants allow the user to tailor the implemented IP core to the selected values, enabling the generation of a lower area/memory occupation version of the IP core. Run-time configuration is implemented by writing to memory-mapped registers.

Verification and validation

The CCSDS-121 and CCSDS-123 IP cores have been extensively verified reference software implementations from ESA and Universitat Autònoma de Barcelona (UAB), proving that, provided the same inputs, the IP cores and software counterparts produce the same exact compressed files.

Technology mapping results

The IP cores have been successfully mapped to the following technologies:

- One-time programmable FPGAs from the RTAX family.

- Reprogrammable FPGAs:

- Xilinx: Virtex5, Virtex6, Virtex7

- Microsemi: RTG4, ProASIC3

- ASIC DARE 180 nm

The hardware occupancy and frequency depend highly on the user-selected compile-time configuration parameters.

The CCSDS-123 exhibits a maximum LUTs/DSPs occupancy of 7% of the Virtex5 FX130 and 13% of the RTG4. The memory requirements depend highly on the selected compile-time parameters and compression order.

The CCSDS-121 IP is comparatively less complex than the CCSDS-123 IP. The FPGA resource use for the Virtex5 is rather low, with a maximum of 3% of LUTs of the Virtex5 FX130.

Extensive configuration examples and detailed mapping results for different technologies are provided in the Product Datasheet and the Summary Report.

Current version

Release.

Developers

University of Las Palmas de Gran Canaria, 2017

Special licensing restrictions

None.