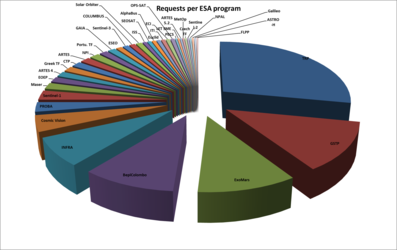

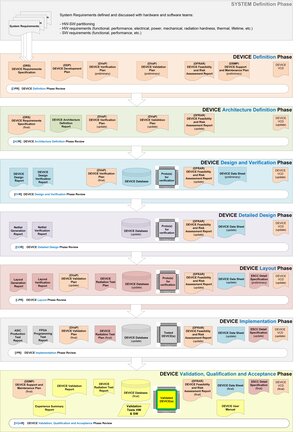

ESA HDL IP Cores Portfolio Overview

This list summarizes the IP cores that can be currently licensed by ESA and those that are under development and will be released in the near future.

All the listed IP Cores are available in synthesizable VHDL with the exception of the RT53EU, which is available in generic technology netlist format. For more information about the IP Cores that are currently under development, please send an e-mail to ipcorerequest@esa.int.

CAN

CAN

- The HurriCANe 5.2.4 comprises the following elements: CAN core, CAN controller, and AMBA APB wrapper (to integrate the CAN core into a system-on-chip).

- Developer: ESTEC/ESA, Aurelia Microelettronica S.p.A. - 1999

CCIPC

- The CANopen Controller IP Core (CCIPC) implements a large subset of the CANopen services as defined in the CAN in Automation (CiA) Standard “CANopen Application Layer and Communication Profile”.

- Developer: Sitael - 2012

SpaceWire and SpaceFibre

SpWB

- SpaceWire codec.

- Developer: University of Dundee - 2013

SpW-AMBA

- SpaceWire Encoder/Decoder with FIFOs (for Xilinx Virtex-E technology) and AMBA AHB master/slave interfaces.

- Developer: Astrium SAS - 2001

SpW-RMAP-Astrium

- The SpaceWire-RMAP IP core implements the Remote Memory Access Protocol (RMAP) extensions to SpaceWire.

- Developer: Astrium - 2008

SpW-RMAP-Dundee

- The SpaceWire-RMAP IP implements the Remote Memory Access Protocol (RMAP) extensions to SpaceWire.

- Developer: University of Dundee - 2009

SpWTDP

- The Time Distribution Protocol (TDP) synchronizes time across a SpaceWire network.

- Developer: Aeroflex Gaisler - 2014

SpW-Node

- Multi-protocol SpaceWire Node IP-core.

- Developer: Teletel S.A. - For more information, please contact the ESA IP Cores service.

SpFi-Port-Gaisler

- SpaceFibre IP.

- Developer: Cobham Gaisler - 201

SEE Mitigation

EDAC

- The EDAC (Error Detection And Correction) IP Core is a set of encoders/decoders supporting data widths from 4 to 64 bits.

- Developer: Surrey Satellite Technology, ESTEC/ESA - 2000

Processors

LEON2-FT

- The LEON2-FT processor is the SEU (Single Event Upset) tolerant version of the LEON2 processor. Flip-flops are protected by Triple Modular Redundancy and all internal and external memories are protected by EDAC or parity bits.

- Developer: ESTEC/ESA, Gaisler Research - 1999

Memory Controllers

FTADDR

- Fault tolerant DDR controller.

- Developer: Cobham Gaisler, 2020

On-Chip Communication

AHBR

- The AHBR IP-Core implements an AMBA AHB to AMBA AHB bus bridge, where the two busses are clock synchronous clocks with defined frequency ratio function.

- Developer: Astrium - 2008

IPMON

- The IP Monitoring (IPMON) module is used to spy an AHB Bus, recording trace and statistics data.

- Developer: Astrium - 2008

NoC [UNDER VALIDATION]

- Network on Chip (NoC) for many-core System on Chip.

- Developer: Recore Systems - Expected 2018

CCSDS data compression

SHyLoC

- Bundle with two IP Cores:

- SHyLoC-121: Universal lossless compression IP Core compliant with the CCSDS-121 standard.

- SHyLoC-123: Multispectral and hyperspectral lossless compression IP Core compliant with the CCSDS-123 standard.

- Developer: University of Las Palmas de Gran Canaria - 2018

CCSDS time keeping, packet telemetry and telecommand

CUC-CTM

- The CCSDS Unsegmented Code (CUC) provides basic time keeping functions such an Elapsed Time counter according to the CCSDS Unsegmented Code specification.

- Developer: ESTEC/ESA - 2000

PDEC

- The PDEC (Packet Telecommand Decoder) comprises a complete CCSDS packet telecommand decoder (PDEC3), a Command Pulse Distribution Module (CPDM), and a Command Pulse Distribution Selector (CSEL), all of them being integrated in an AMBA AHB wrapper.

- Developer: Gaisler Research - 2003

PTCD

- The Packet Telecommand Decoder (PTCD) IP Core is a model of the MA28140 chip from GEC-Plessey Semiconductors.

- Developer: Astrium SAS - 2002

PTME

- The Packet Telemetry Encoder (PTME) comprises a complete CCSDS packet telemetry encoder.

- Developer: ESTEC/ESA, Gaisler Research - 1999

SCCC IP Core

- IP Core for Medium Data Rate PDT compliant with CCSDS 131.2-B standard.

- Developer: IngeniArs S.r.l. - 2018

Authentication and encryption

AUIP

- The Authentication Unit (AU) Intellectual Property (IP) contains functionality for Telecommand (TC) authentication using the Advanced Encryption Standard (AES). The functionality also includes Key management and Logical Authentication Channel (LAC) management.

- Developer: RUAG Space AB - 2010

Mil-Std-1553

IP1553

- The IP1553 IP core implements a Mil-Std-1553 interface. It is compatible with the MIL-STD-1553B (notice 2) protocol and manages three different working modes: Bus Controller, Remote Terminal, and Bus Monitor.

- Developer: Astrium SAS

RT53EUR

- MIL-STD-1553B Remote Terminal IP Core. Delivered as a generic technology netlist format.

- Developer: Astrium SAS - 2009

Germany

Germany

Austria

Austria

Belgium

Belgium

Denmark

Denmark

Spain

Spain

Estonia

Estonia

Finland

Finland

France

France

Greece

Greece

Hungary

Hungary

Ireland

Ireland

Italy

Italy

Luxembourg

Luxembourg

Norway

Norway

The Netherlands

The Netherlands

Poland

Poland

Portugal

Portugal

Czechia

Czechia

Romania

Romania

United Kingdom

United Kingdom

Slovenia

Slovenia

Sweden

Sweden

Switzerland

Switzerland