Fault Tolerant DDR Controller (FTADDR)

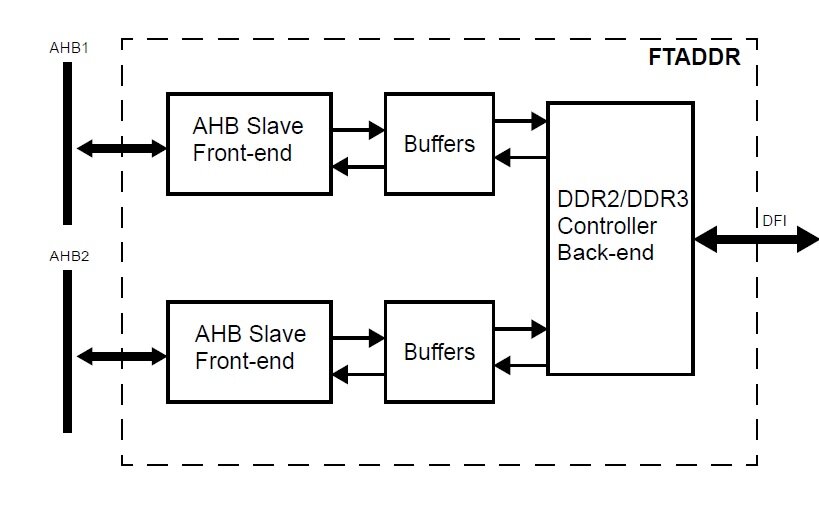

FTADDR is a memory controller for DDR2 and DDR3 type of SDRAM memory devices. On the memory side, it presents a DFI interface for connection to an on-chip physical layer (PHY) that manages the low-level timing and data recovery and then provides the I/O buffers. Towards the systemon-chip, it presents the memory through an AMBA AHB slave interface.

Overview

Internally, the controller is composed of one part clocked by the AMBA clock which manages the user interface, one part clocked by the DFI clock to manage DDR command scheduling and initialization, and FIFOs to communicate between these two parts. The controller is designed to interface 96-bit wide banks of memory, made out of individual memory devices of width x8 or x4, and then uses a strong error correction code to achieve double-device correction capability. This allows it to deliver correct data despite one full device failure and random SEU-induced errors on the other devices. Up to 8 parallel banks (chip selects) are supported by the controller. Reduced configurations are possible for reduced pin count. The controller can be used in a multi-ported configuration to support concurrent accesses to different memory banks.

The controller provides configuration registers accessed through a separate address area in the AHB slave. The controller is designed to support processor-less configurations and therefore can operate autonomously with the desired configuration settings supplied as input data at system reset. An interface for direct control of DDR commands and diagnostic reading of data and checkbits is also provided.

Technology mapping

Synthesis was done on C65SPACE, and scripts are provided. C65SPACE technology libraries and macrocells (memories, PHY) are not provided within the IP. C65SPACE technology specific RAMs can be easily replaced by RAMs in other target technology or by inferred RAMs.

Developers

Cobham Gaisler, 2020

Special licencing restrictions

No special licensing conditions apply. For more information refer to the ESA IP-Cores licensing page.