PTME

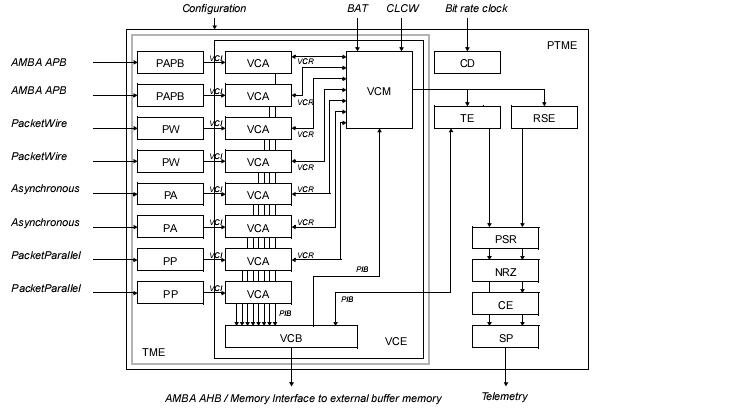

The Packet Telemetry Encoder (PTME) is a synthesizable VHDL IP core, comprising a complete CCSDS packet telemetry encoder. It includes the following blocks:

- Virtual Channel Assemblers, associated to various input interfaces (Packet-APB, Packet-Wire, Packet-Asynchronous-RS232 and Packet-Parallel),

- Virtual Channel Multiplexer, and

- Telemetry encoder chain (including Reed-Solomon encoder, and Convolutional encoder).

The core is highly configurable at compile (synthesis) time and at runtime, and it is extensively documented.

Overview

The PTME is a synthesizable VHDL model. It comprises several encoders and modulators implementing the Consultative Committee for Space Data Systems (CCSDS) recommendations and the European Space Agency (ESA) Procedures, Standards and Specifications (PSS) for telemetry and channel coding. The Packet Telemetry Encoder (PTME) VHDL model comprises the following:• Telemetry Encoder (TME)

• Reed-Solomon Encoder (RSE)

• Non-Return-to-Zero Mark encoder (NRZ)

• Pseudo-Randomiser (PSR)

• Convolutional Encoder (CE)

• Split-Phase Level modulator (SP)

• Clock Divider (CD)

The Telemetry Encoder (TME) implements the AD1 and AD2 telemetry standards. The VHDL model implementing the TME is possible to configure to support from 1 to 8 Virtual Channels (VCs).

The Reed-Solomon Encoder (RSE) implements encoding according to the AD3 and AD4 channel coding standards.

The Turbo Encoder (TE) implements encoding according to the AD4 channel coding recommendation.

The Pseudo-Randomiser (PSR) implements encoding according to the AD3 and AD4 channel coding standards.

The Convolutional Encoder (CE) implements encoding according to the AD3 and AD4 channel coding standards.

The Non-Return-to-Zero Mark encoder (NRZ) and Split-Phase Level modulator (SP) implements signal modulation according to the AD5 standard.

The Clock Divider (CD) generates the bit rates and clock enable signals for the different encoders and modulators above.

The European Cooperation for Space Standardization (ECSS) documents will be based on the CCSDS recommendations, permitting the PTME to be used in future projects.

The PTME is being used in two ongoing ESA satellite projects and in several microelectronics developments.

The PTME model is based on the knowledge and experiences from the preceding VCA, VCM and RESCUE standard devices.

Area/Speed Results

Synthesis results of SCOC-PTME version 0.4a (without I/O insertion)

Xilinx Virtex-II 1000, -6 : 6385 (62%) LUT, 4006 (39%) FF, 37 MHz

Actel AX2000, -3 : 6944 (32%) COMB, 4167 (39%) SEQ, 29 MHz

13 external I/O's

Developer

Sandi Habinc, ESTEC/ESA, 1999

Current Release

version 0.8e, May 2007

Special licensing restrictions

None